# The Parametric Measurement Handbook 4th Edition

# Table of Contents

| Table of Contents                                                   |    |

|---------------------------------------------------------------------|----|

| Preface                                                             |    |

| Chapter 1 – Keysight Technologies' Parametric Measurement Solutions |    |

| What is a parametric test?                                          |    |

| Why is parametric testing performed?                                |    |

| Where is parametric testing done?                                   |    |

| Parametric instrument history                                       |    |

| The 1980's                                                          |    |

| The 1990's                                                          |    |

| The 21st century                                                    |    |

| Chapter 2 – Parametric Measurement Basics                           |    |

| Measurement terminology                                             |    |

| Accuracy and repeatability                                          |    |

| Resolution                                                          |    |

| Traceability                                                        |    |

| Shielding and guarding                                              |    |

| Shielding: Maintaining a low noise floor                            |    |

| Avoiding ground loops                                               |    |

| Guarding: Isolation for low-current measurement                     |    |

| Connecting triaxial and BNC cables                                  |    |

| Kelvin (4-wire) measurements                                        |    |

| Kelvin triaxial cables                                              |    |

| Noise in electrical measurements                                    |    |

| Shot noise                                                          |    |

| Thermal noise                                                       |    |

| Flicker or 1/f noise                                                |    |

| Random Telegraph Noise (RTN)                                        |    |

| Power line cycle noise                                              |    |

| Chapter 3 – Source/Monitor Unit (SMU) Fundamentals                  |    |

| SMU overview                                                        |    |

| Introduction                                                        |    |

| SMU operation modes and settings                                    |    |

| SMU force and sense outputs                                         |    |

| Understanding the ground unit                                       |    |

| High current SMU connections (B1505A and B1506A)                    |    |

| Medium Current SMU Connections (B1500A)                             |    |

| Measurement ranging                                                 |    |

| Measurement ranging basics                                          | 45 |

| Measurement range management                                        |    |

| Eliminating measurement noise and signal transients                 |    |

| Integration time                                                    |    |

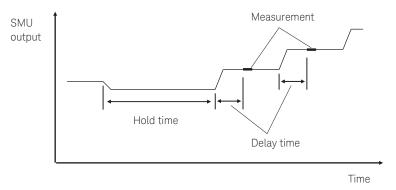

| Hold time and delay time                                            |    |

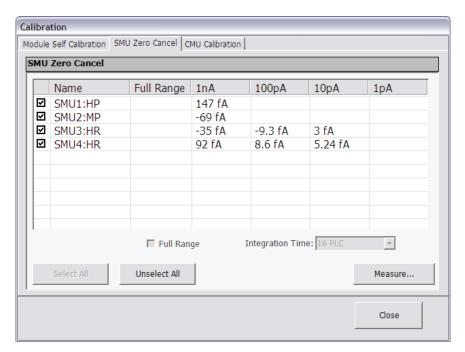

| SMU zero cancel function                                            |    |

| Debugging low current measurements                                  |    |

| Spot and sweep measurements                                         |    |

| Spot versus sweep measurements                                      |    |

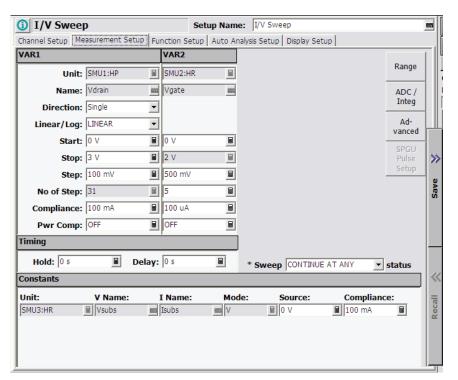

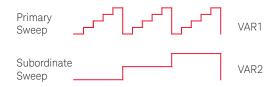

| Primary sweep measurement                                           |    |

| Pulsed sweep measurement                                            |    |

| Subordinate sweep measurement                                       |    |

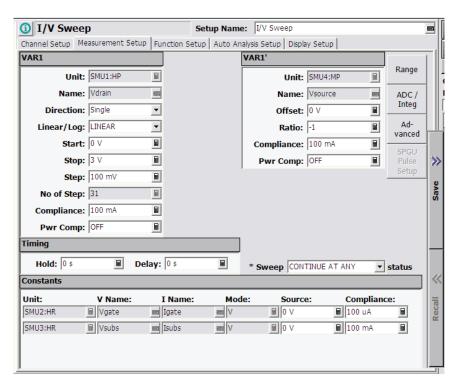

| Synchronized sweep measurement                                      |    |

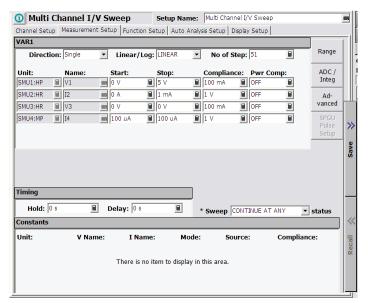

| Multi-channel sweep measurement                                     |    |

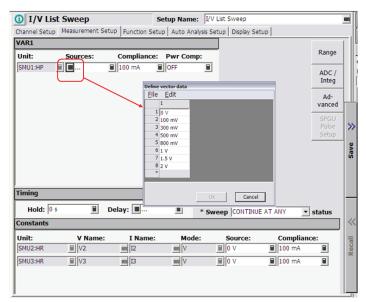

| List sweep measurement                                              | 62 |

|                                                                     |    |

# Table of Contents (continued)

| Combining SMUs in series and parallel                     |    |

|-----------------------------------------------------------|----|

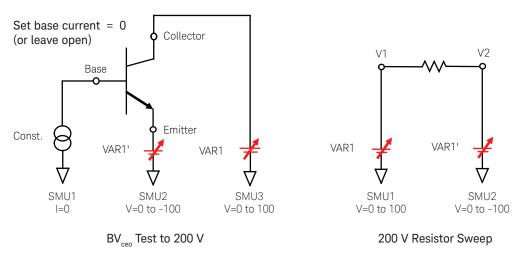

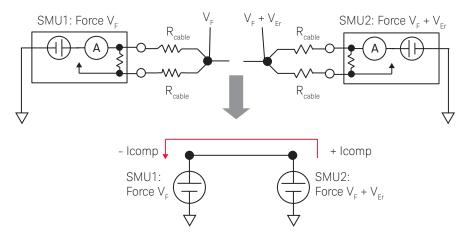

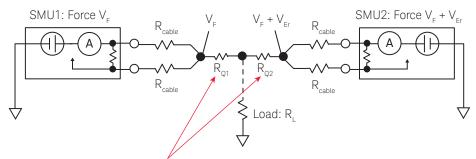

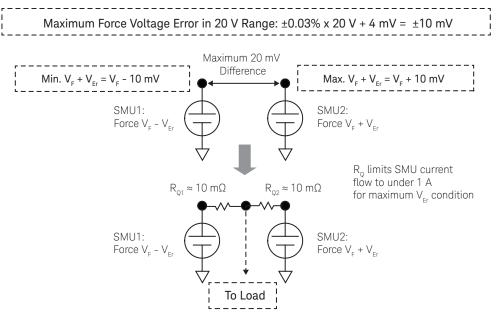

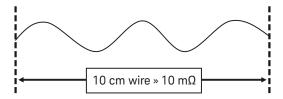

| Combining SMUs in series                                  | 63 |

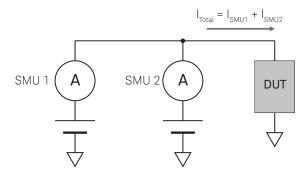

| Combining SMUs in parallel                                | 64 |

| Combining two HCSMUs in parallel                          | 66 |

| Safety issues                                             | 67 |

| Interlock                                                 |    |

| Additional Modules and Accessories for Power Device Test  | 7C |

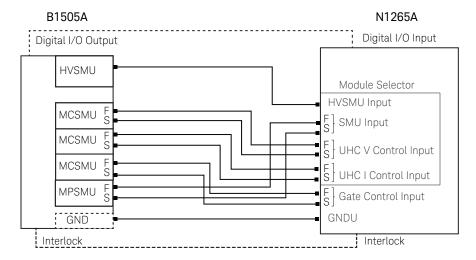

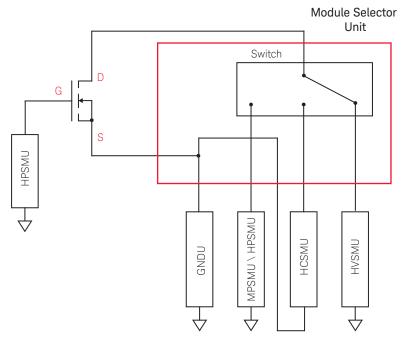

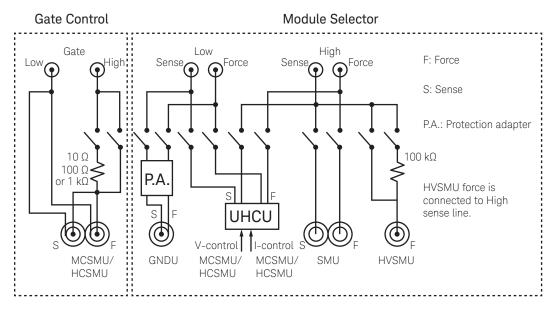

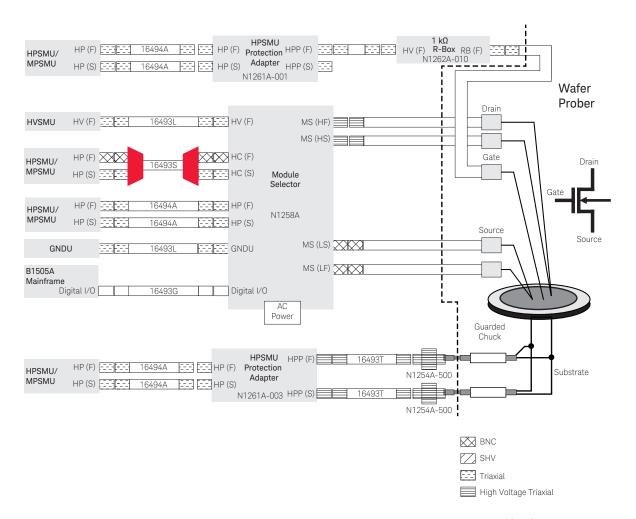

| Module selector unit                                      | 7C |

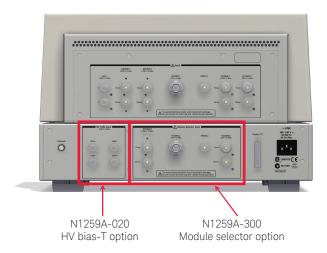

| High-voltage Bias-T                                       |    |

| High-voltage SMU current expander                         | 73 |

| Ultra-high voltage unit (10 kV)                           | 73 |

| Summary of B1505A IV options                              |    |

| Chapter 4 – On-Wafer Parametric Measurement               | 75 |

| Introduction                                              | 75 |

| Fully automatic versus analytical wafer probers           | 75 |

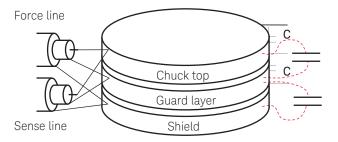

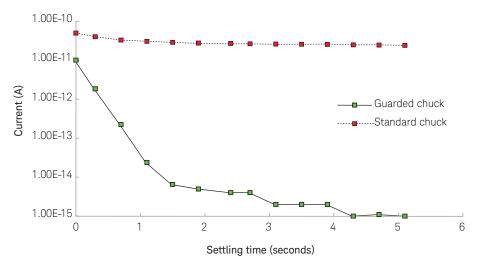

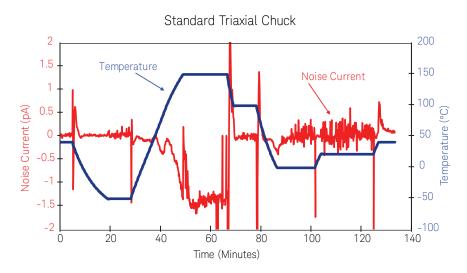

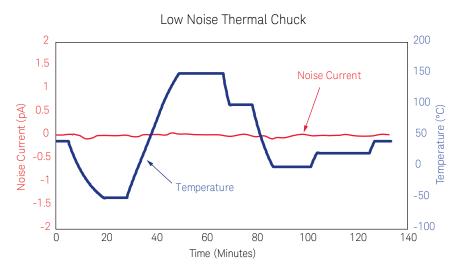

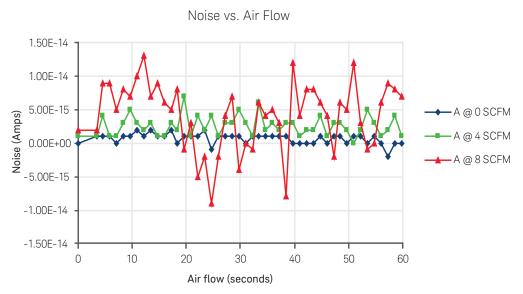

| Wafer prober measurement concerns                         | 76 |

| Chuck isolation                                           | 76 |

| Low and high temperature measurement issues               | 77 |

| DC and RF wafer probes                                    |    |

| Switching matrices                                        |    |

| Introduction                                              | 83 |

| Probe cards and module testing                            |    |

| Reliability Test Switching Solutions                      |    |

| Positioner-based switching solutions                      | 93 |

| Introduction                                              |    |

| Atto-sense and switch unit                                |    |

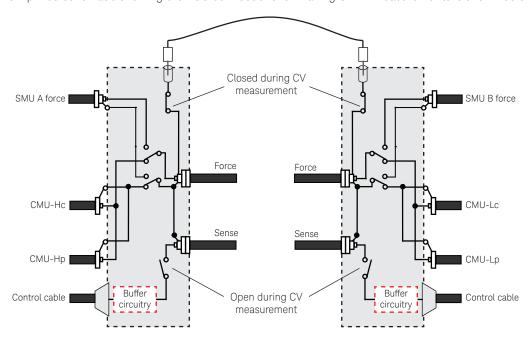

| SMU CMU unify unit                                        |    |

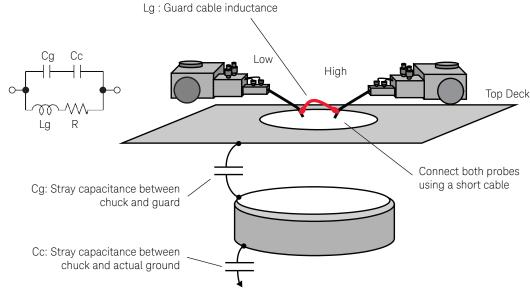

| Shorting the guards together during measurement           |    |

| Summary of Keysight positioner-based switching solutions  |    |

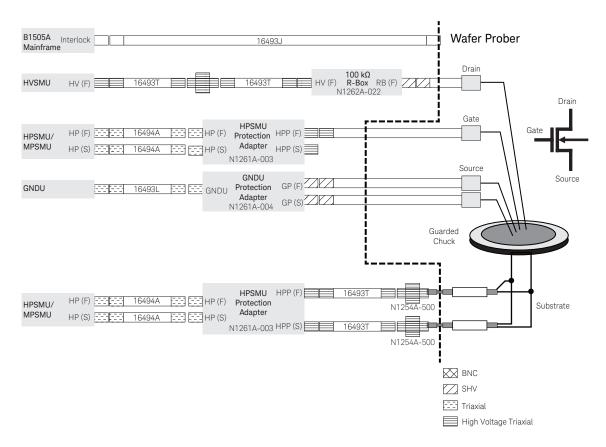

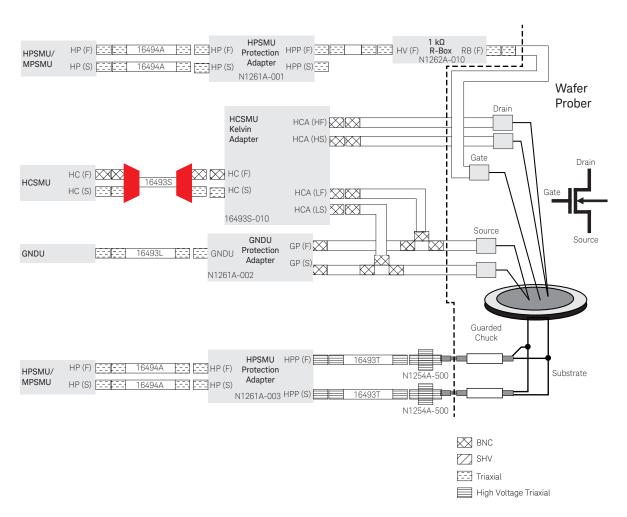

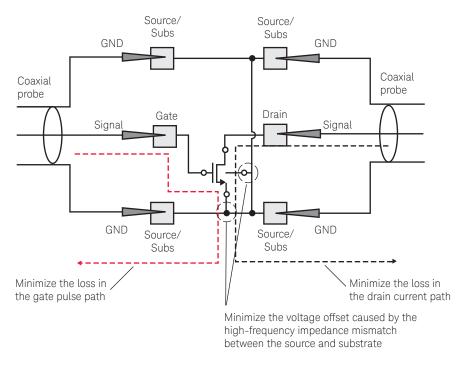

| High voltage and high current wafer probing               |    |

| Overview                                                  |    |

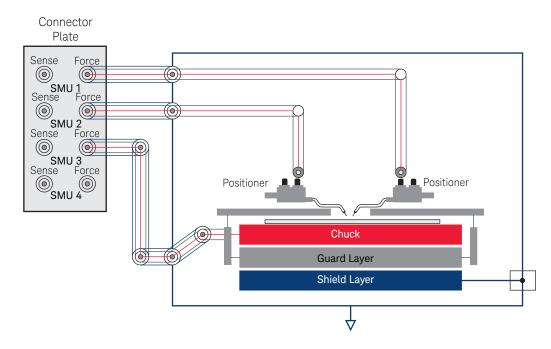

| Connection considerations                                 |    |

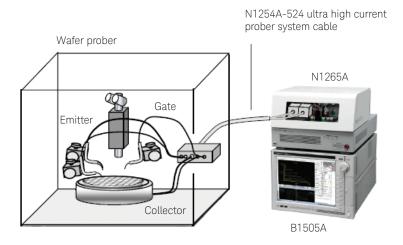

| Prober connections using the N1265A and N1254A-524        |    |

| Chapter 5 – Time Dependent and High-Speed Measurements    |    |

| Introduction                                              |    |

| Parallel measurement with SMUs                            |    |

| Time sampling with SMUs                                   |    |

| Sequential versus synchronous sequencing                  |    |

| Setting up the time sampling interval                     |    |

| Advanced time sampling features (B1500A/05A/06A)          |    |

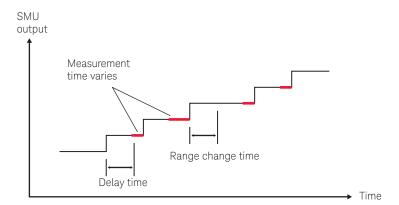

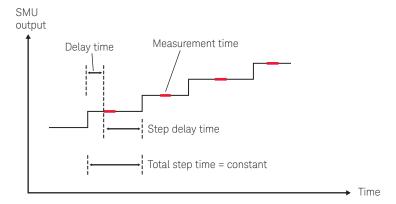

| Maintaining a constant sweep step                         |    |

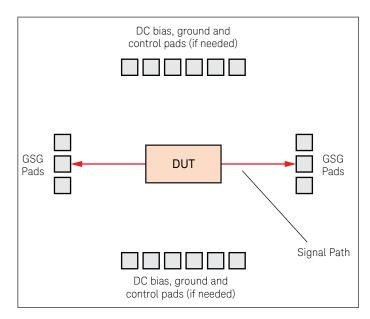

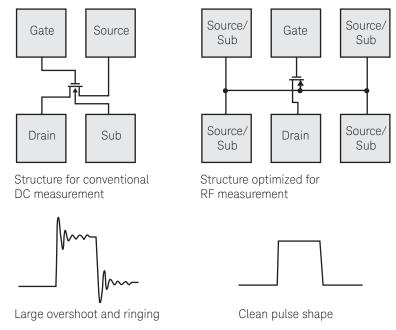

| High speed test structure design                          |    |

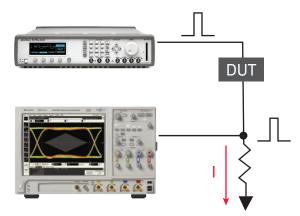

| Fast IV and fast pulsed IV measurements                   |    |

| Overview                                                  |    |

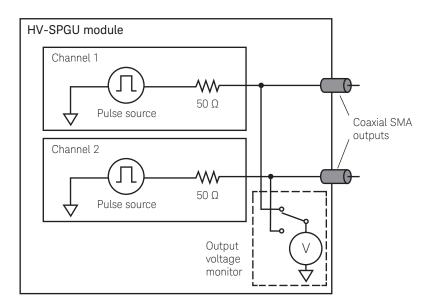

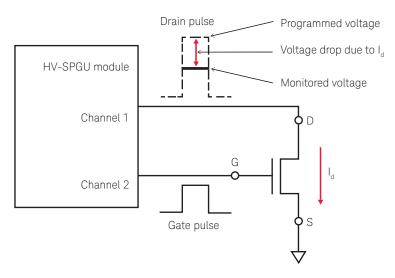

| High-voltage semiconductor pulse generator unit (HV-SPGU) |    |

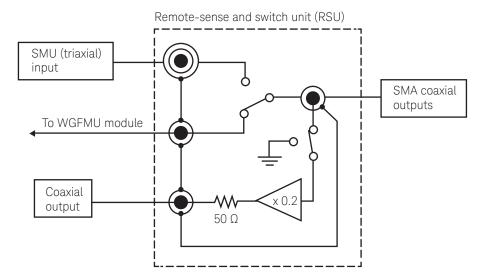

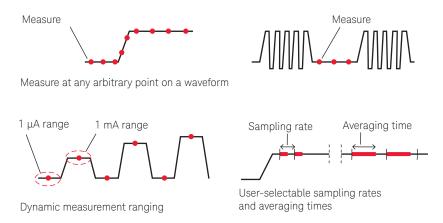

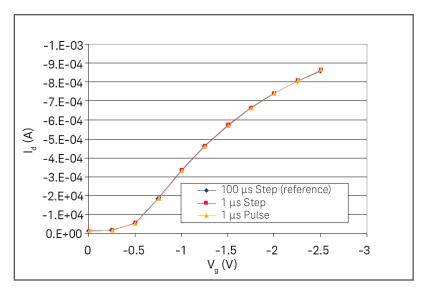

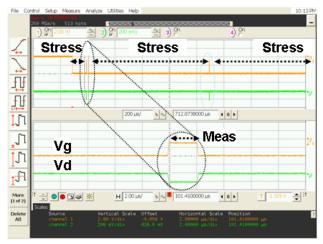

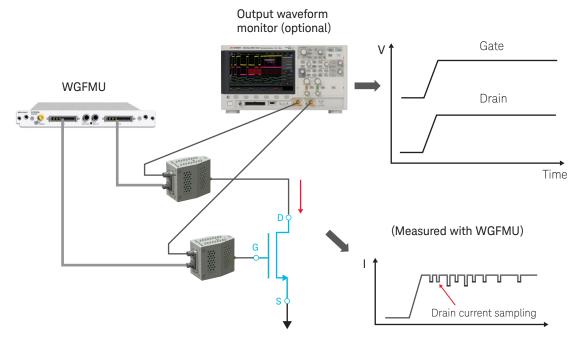

| Waveform generator/fast measurement unit (WGFMU)          |    |

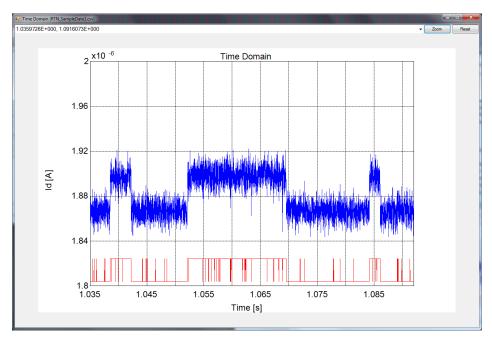

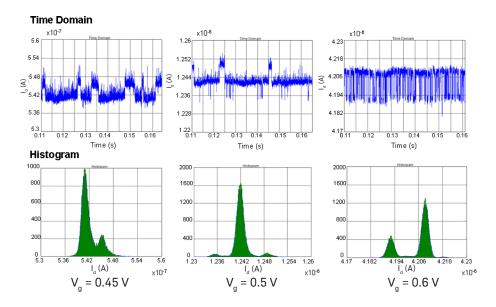

| Random Telegraph Noise (RTN) Measurement                  |    |

| Summary of Keysight pulsed IV measurement solutions       |    |

# Table of Contents (continued)

| Chapter 6 – Making Accurate Resistance Measurements               | 135 |

|-------------------------------------------------------------------|-----|

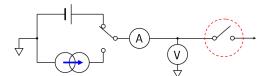

| Resistance measurement basics                                     | 135 |

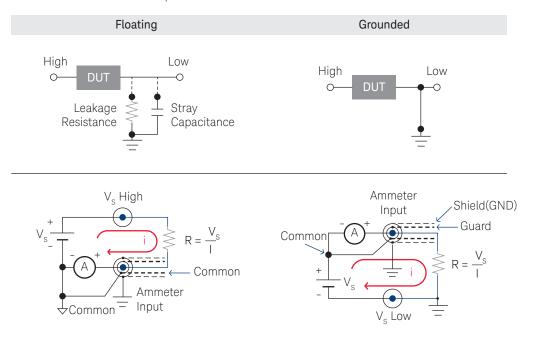

| Floating vs. grounded resistance measurements                     | 136 |

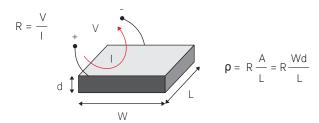

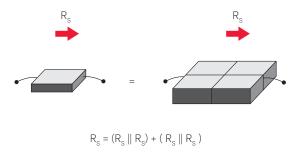

| Resistivity                                                       | 137 |

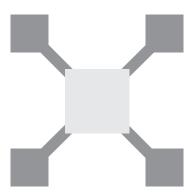

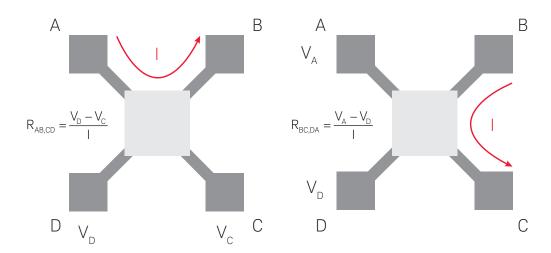

| Van der Pauw test structures                                      | 138 |

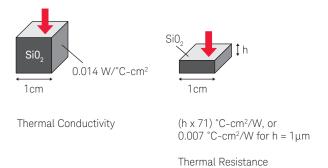

| Accounting for Joule self-heating effects                         | 139 |

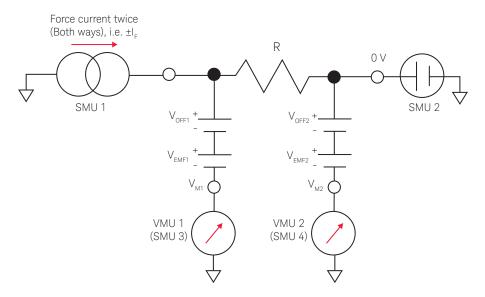

| Eliminating the effects of electro-motive force (EMF)             | 140 |

| What is EMF?                                                      | 140 |

| Mitigating the effects of EMF                                     | 142 |

| Chapter 7 – Diode and Transistor Measurement                      | 143 |

| Introduction                                                      | 143 |

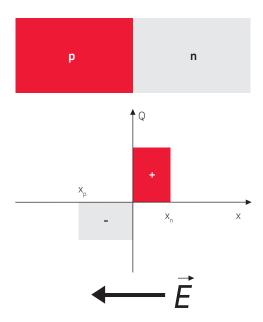

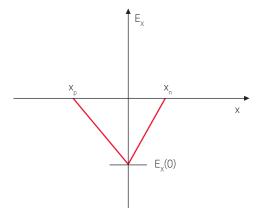

| PN junctions and diodes                                           | 143 |

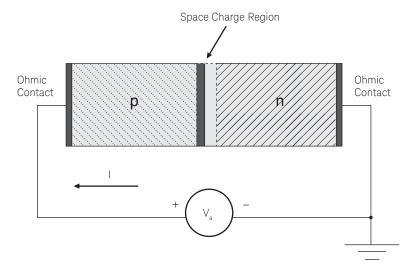

| Review of PN diode operation                                      | 143 |

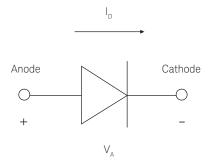

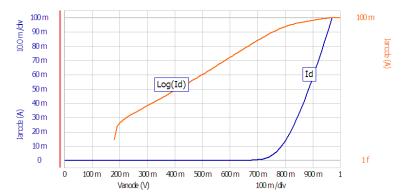

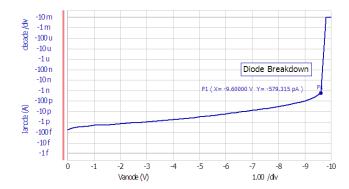

| Basic diode characterization                                      | 148 |

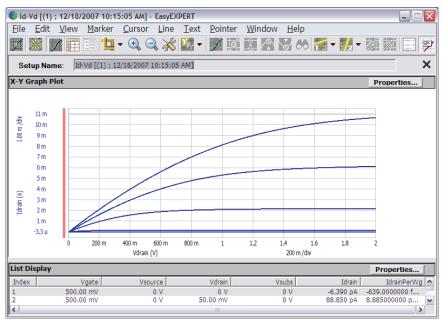

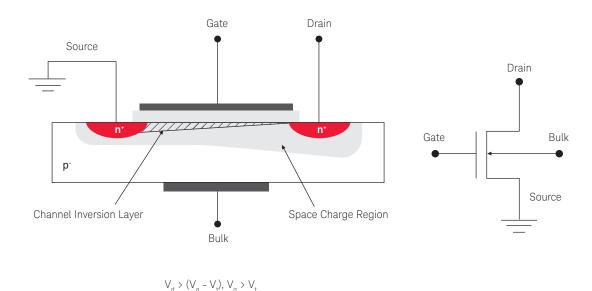

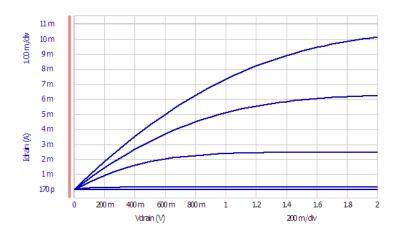

| MOS transistor measurement                                        | 149 |

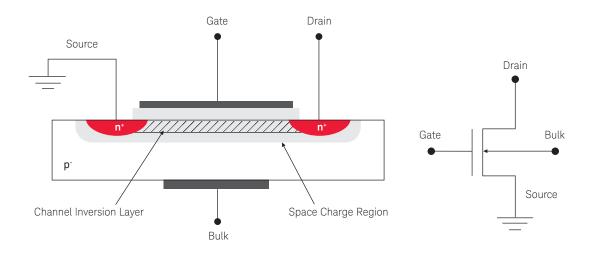

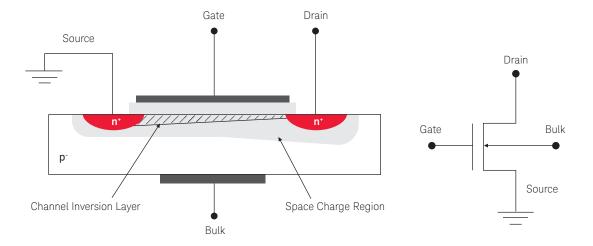

| Review of MOSFET operation                                        | 149 |

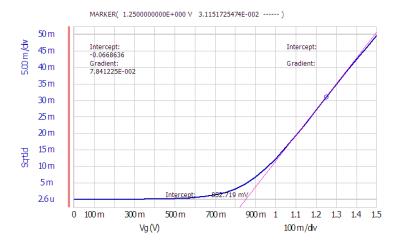

| Basic MOSFET characterization                                     | 154 |

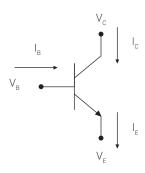

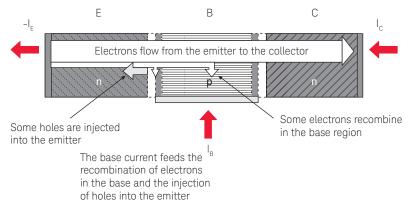

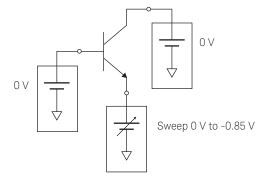

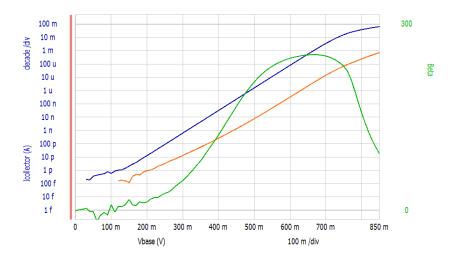

| Bipolar transistor measurement                                    | 157 |

| Review of bipolar transistor operation                            | 157 |

| Basic bipolar transistor characterization                         | 158 |

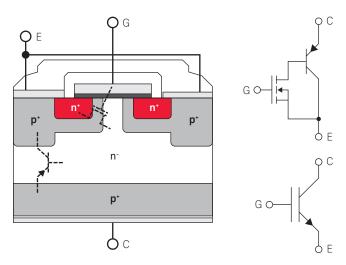

| The insulated gate bipolar transistor                             | 162 |

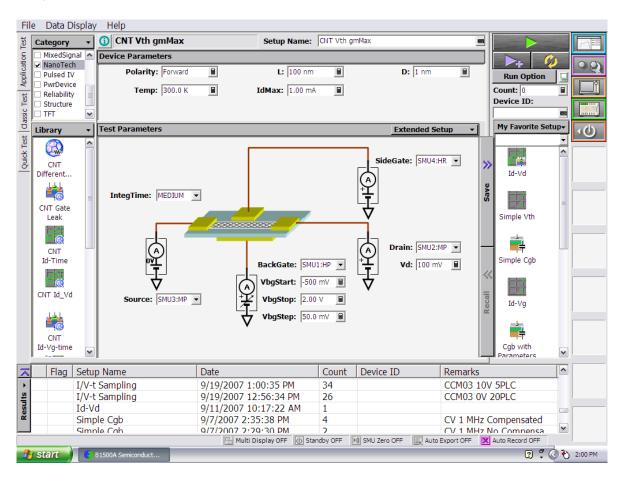

| Nanotech devices                                                  | 163 |

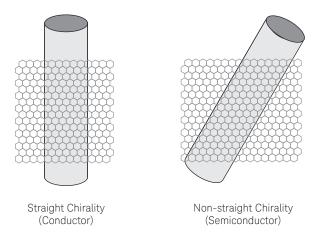

| Carbon nanotubes                                                  | 163 |

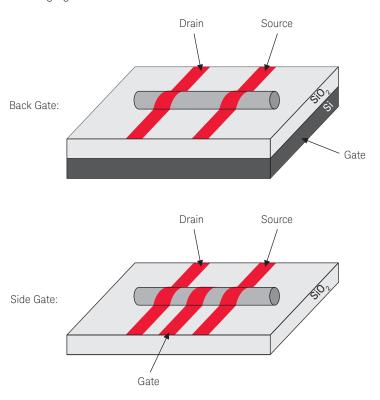

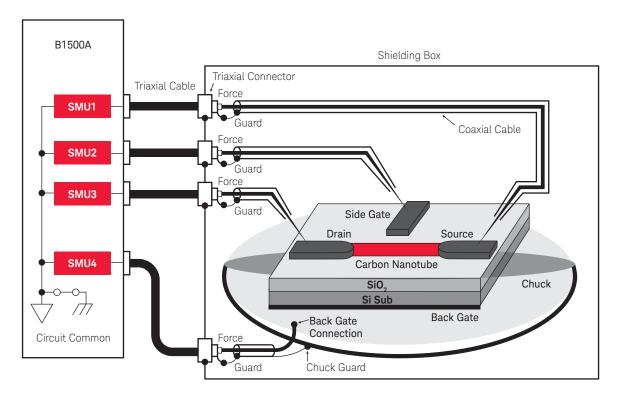

| Carbon nanotube transistors                                       | 164 |

| Chapter 8 – Capacitance Measurement Fundamentals                  | 167 |

| Introduction                                                      | 167 |

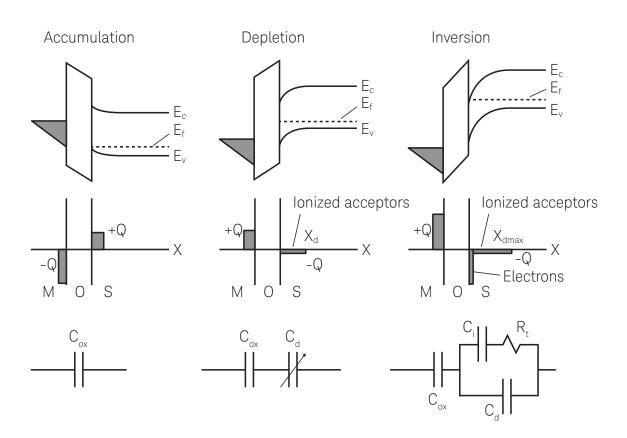

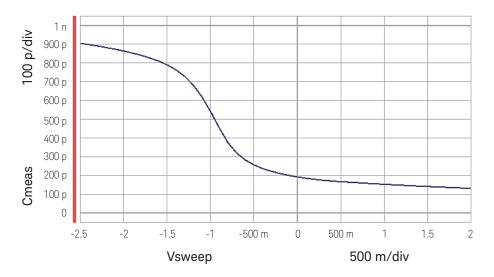

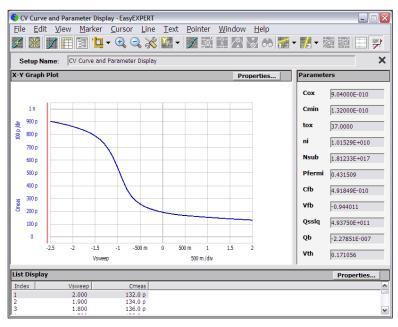

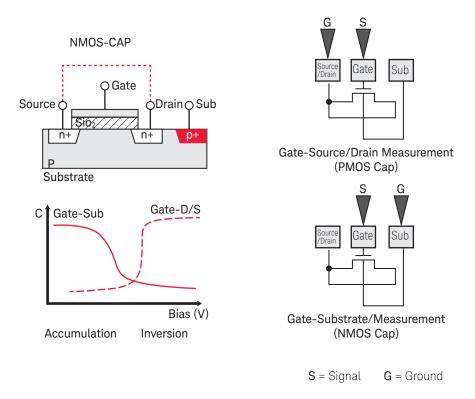

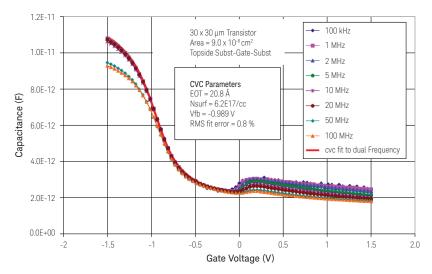

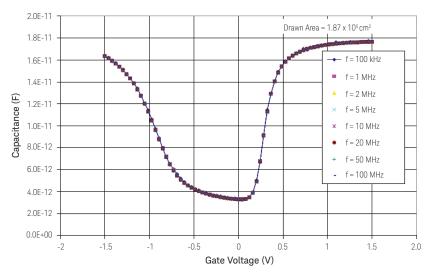

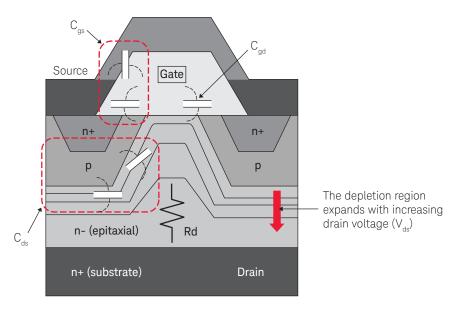

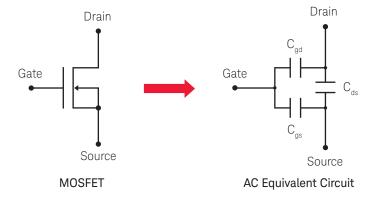

| MOSFET capacitance measurement                                    | 168 |

| Review of MOSFET capacitance behavior                             | 168 |

| Sample MOSFET parameter calculation                               | 169 |

| Quasi-static capacitance measurement                              | 173 |

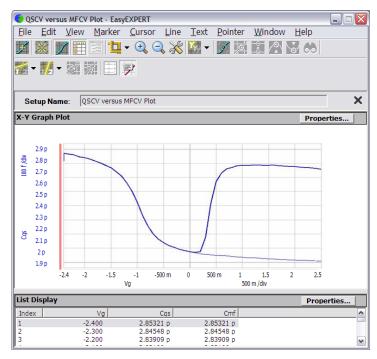

| Obtaining a QSCV response                                         | 173 |

| The voltage ramp QSCV measurement technique                       | 174 |

| The voltage step QSCV measurement technique                       | 175 |

| QSCV offset compensation                                          | 177 |

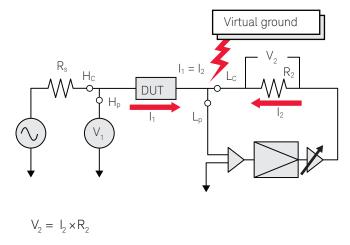

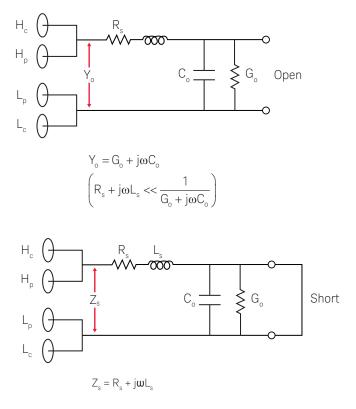

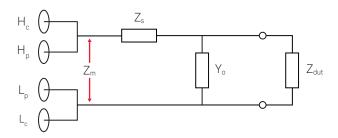

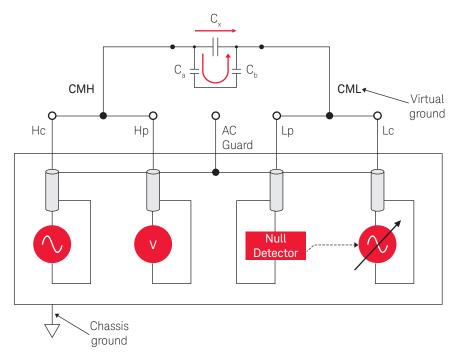

| Low frequency (< 5 MHz) capacitance measurement                   | 178 |

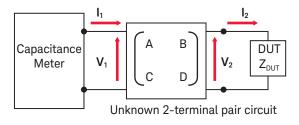

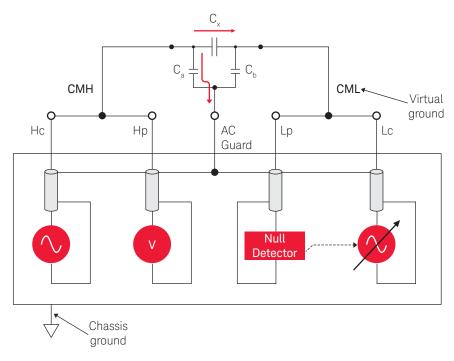

| Capacitance meter operation                                       | 178 |

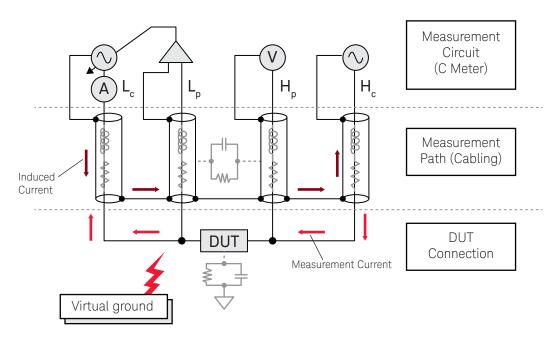

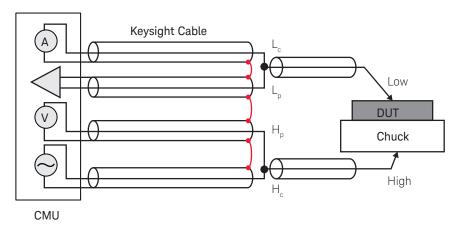

| The 4TP measurement method                                        | 179 |

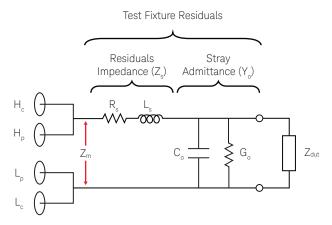

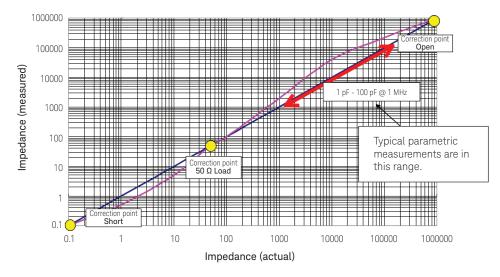

| The importance of proper compensation                             | 180 |

| On-wafer capacitance measurement                                  | 182 |

| High frequency (>5 MHz) capacitance measurement                   | 185 |

| Thin Gate Dielectric Fundamentals                                 | 185 |

| Optimizing CV measurement results through proper structure design | 190 |

| Pad layout considerations                                         | 191 |

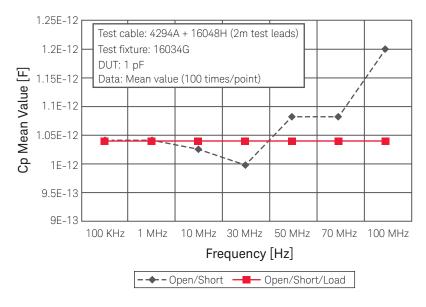

| Open/Short/Load calibration                                       |     |

| Calculating the values of the three element capacitor model       |     |

| The advanced IV method                                            |     |

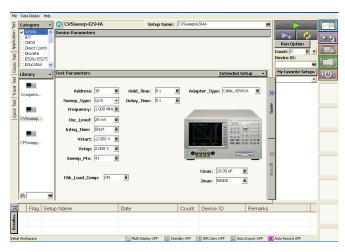

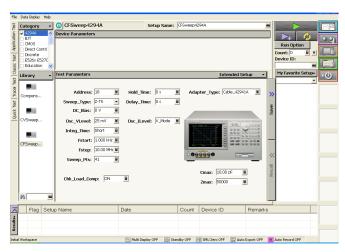

| Controlling the 4294A or E4990A using EasyEXPERT                  | 201 |

| Summary of thin gate dielectric best practices                    |     |

# Table of Contents (continued)

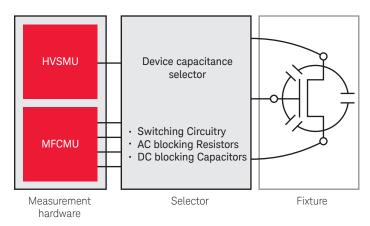

| Making capacitance measurements through a switching matrix           |     |

|----------------------------------------------------------------------|-----|

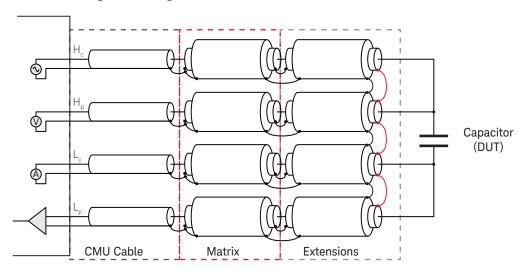

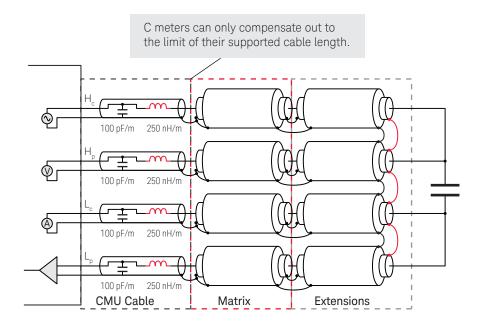

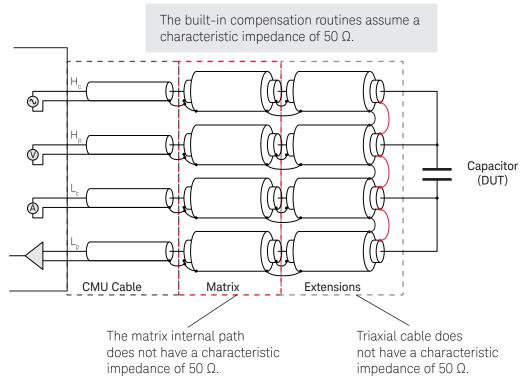

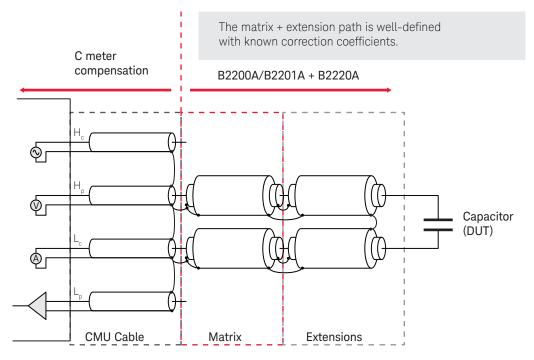

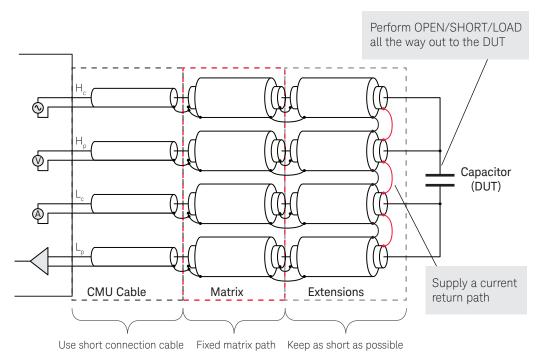

| Switching Matrix Capacitance Measurement Issues                      | 204 |

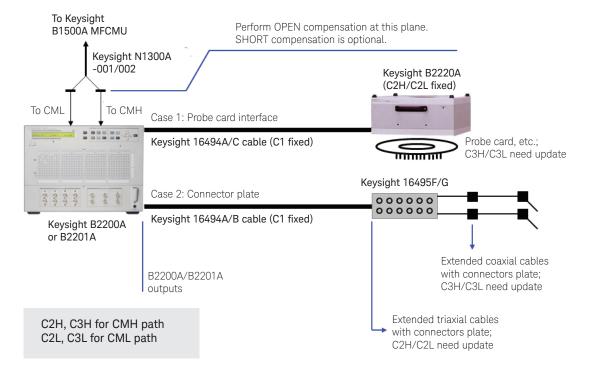

| CMU cable compensation                                               |     |

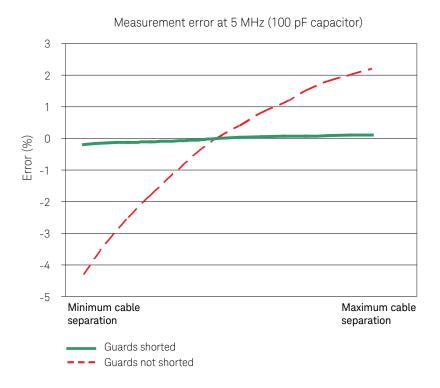

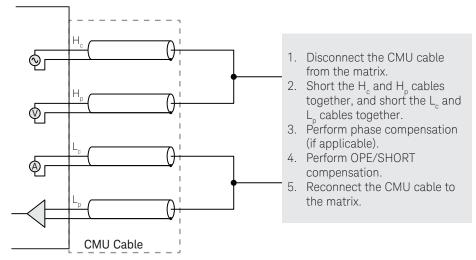

| Shorting the guards                                                  | 206 |

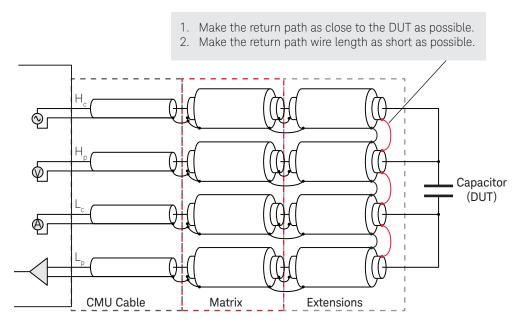

| Impedance mismatch                                                   | 207 |

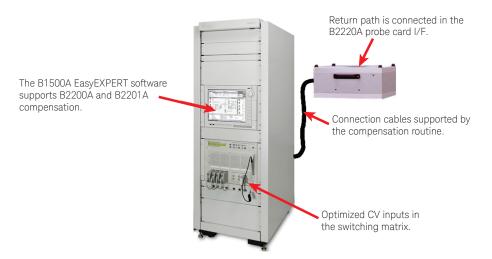

| Keysight's switching matrix solution                                 | 208 |

| Tips for measuring at frequencies above 1 MHz                        | 210 |

| Chapter 9 – Power Device Characterization                            | 211 |

| Introduction                                                         |     |

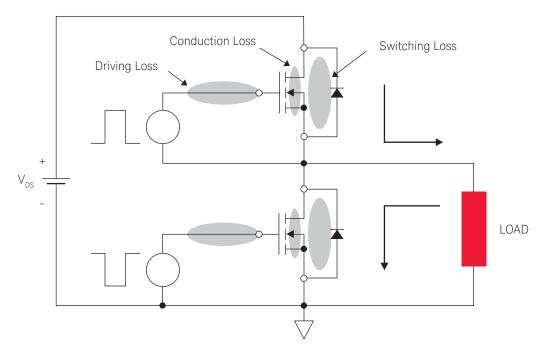

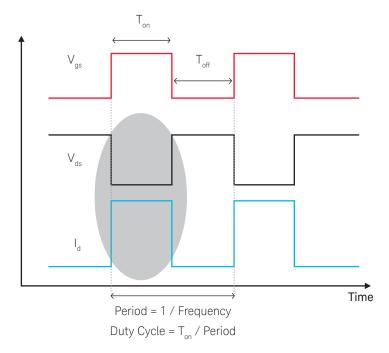

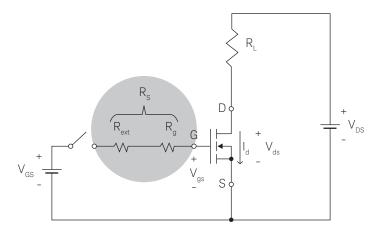

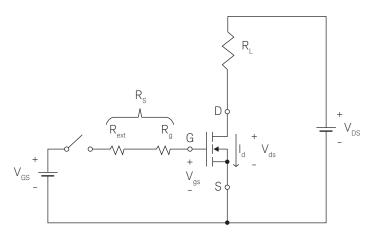

| Calculating Power Loss in Power Semiconductor Devices                | 211 |

| Conduction loss                                                      | 212 |

| Driving loss                                                         | 213 |

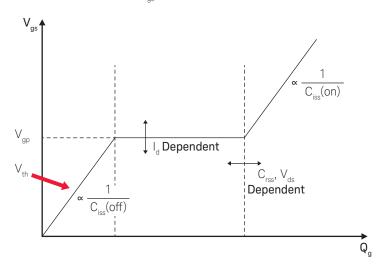

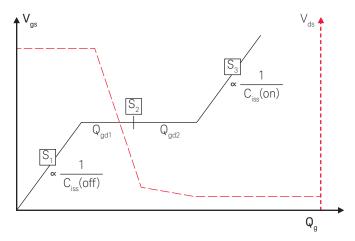

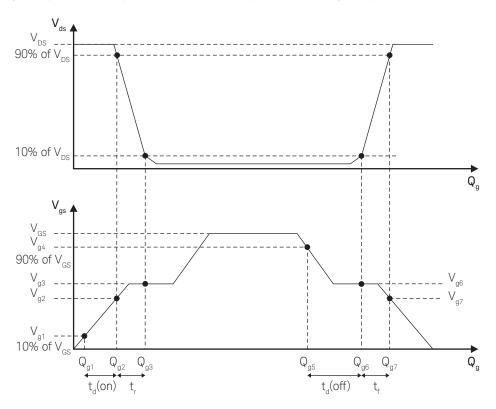

| Gate charge overview                                                 | 213 |

| Gate charge equations by region                                      | 213 |

| Gate charge switching time equations                                 | 213 |

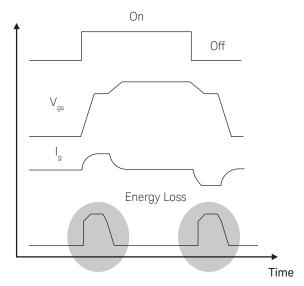

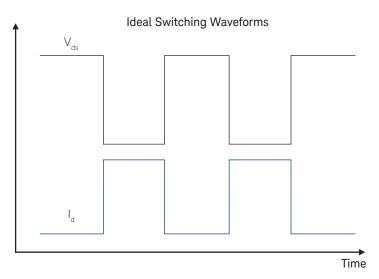

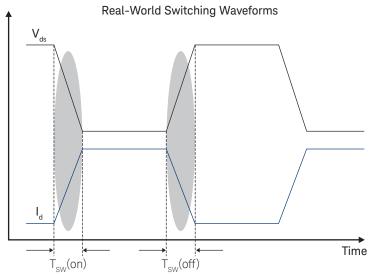

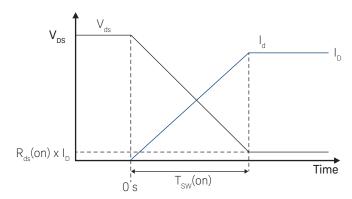

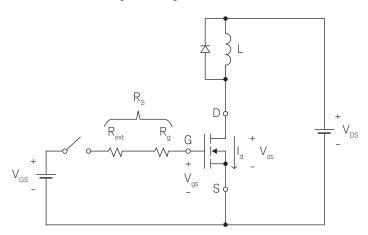

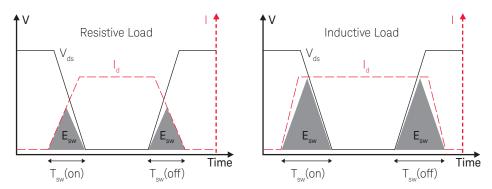

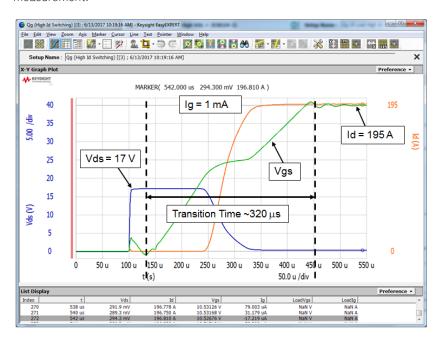

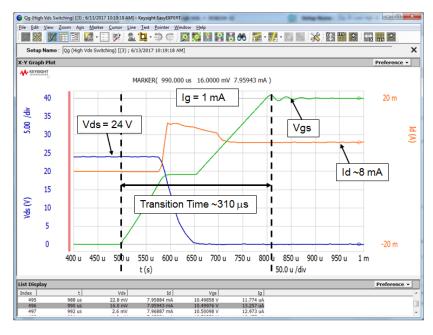

| Switching loss                                                       | 218 |

| Resistive load switching loss                                        | 218 |

| Inductive load switching loss                                        | 218 |

| Summarized switching loss equations                                  | 222 |

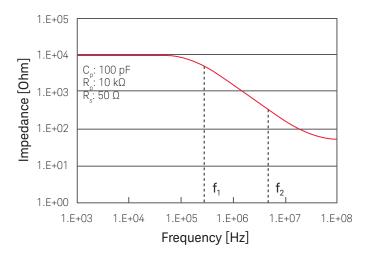

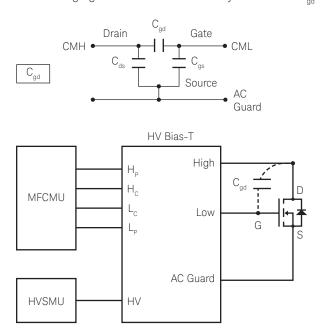

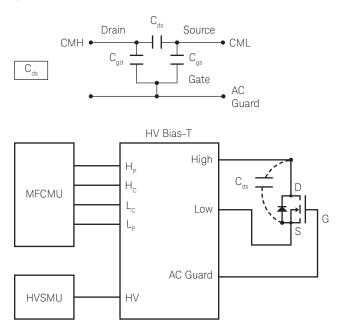

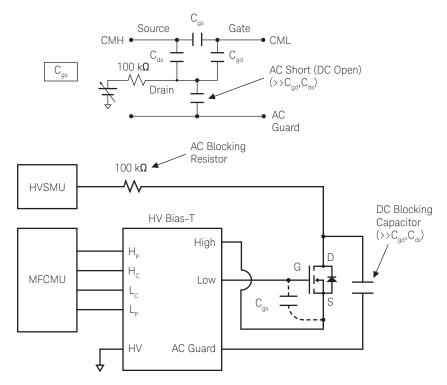

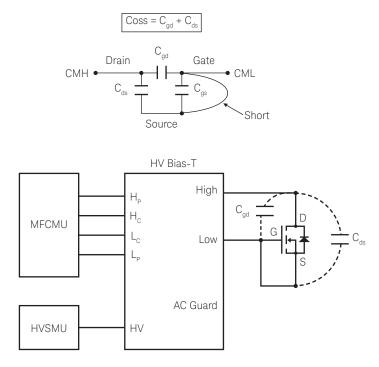

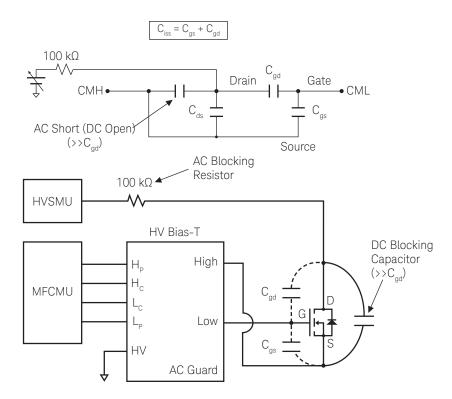

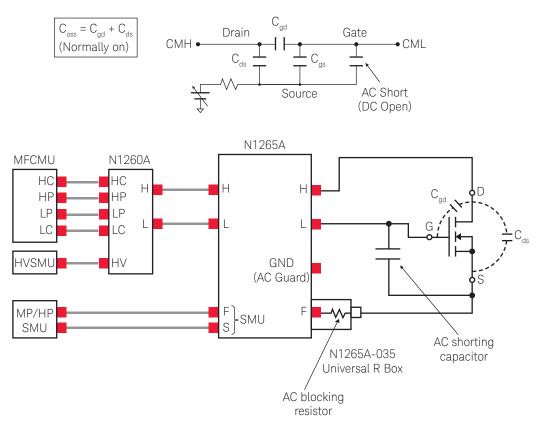

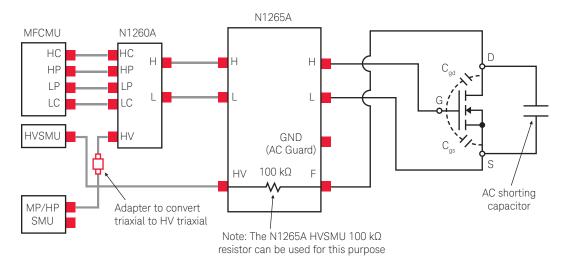

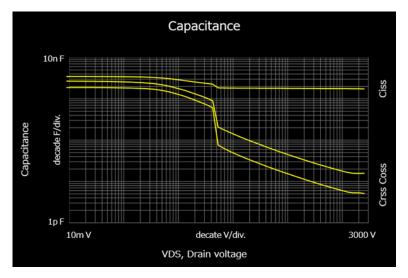

| High DC bias capacitance measurements                                | 223 |

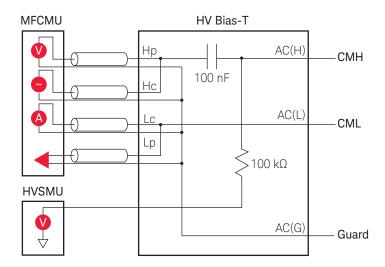

| High-Voltage Bias-T                                                  |     |

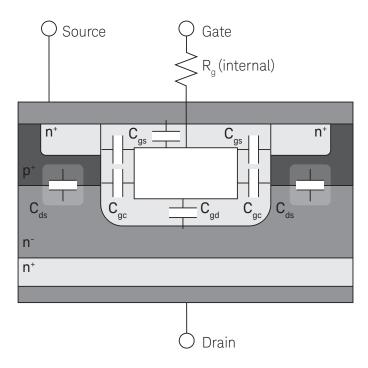

| High-power MOSFET capacitance measurement                            |     |

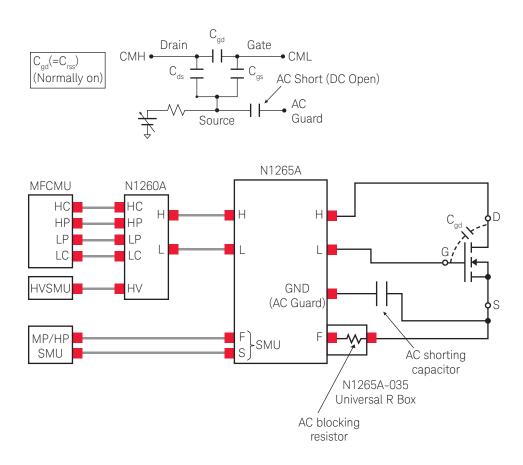

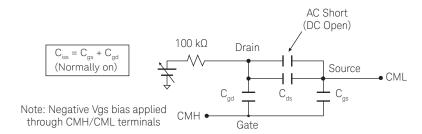

| Measuring capacitance of "normally on" devices                       |     |

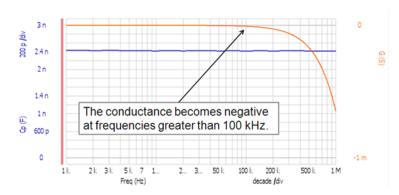

| High-power capacitance measurement frequency issues                  |     |

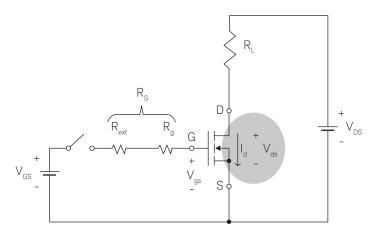

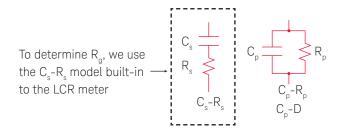

| Measuring gate resistance                                            |     |

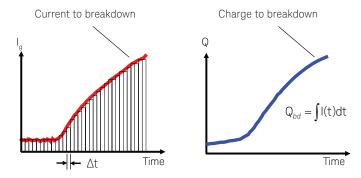

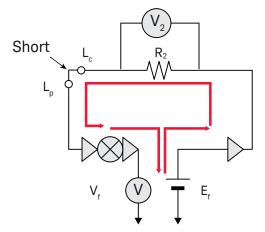

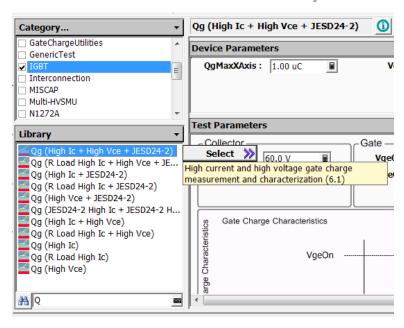

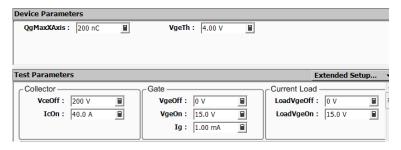

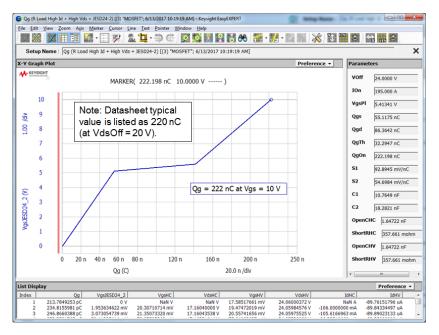

| Gate charge measurement                                              |     |

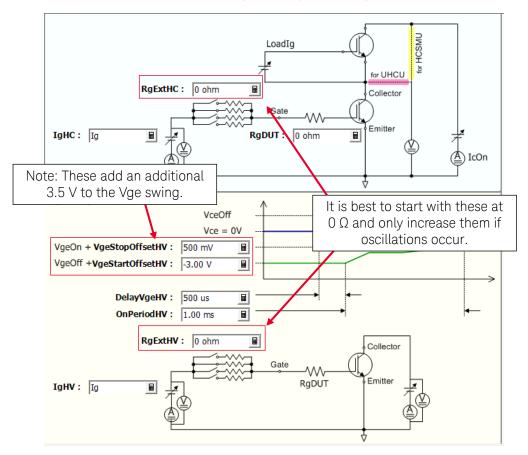

| The two-pass (HV/HC) gate charge measurement technique               |     |

| Gate charge test fixture overview                                    |     |

| Gate charge test fixture calibration and setup                       |     |

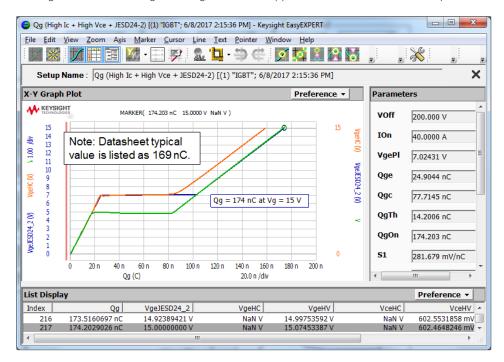

| Gate Charge Measurement on a Silicon IGBT                            |     |

| Gate charge measurement using UHCU with R-load                       |     |

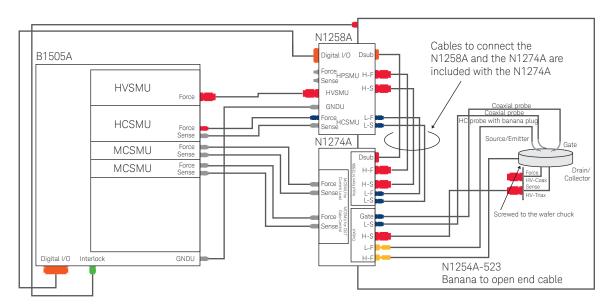

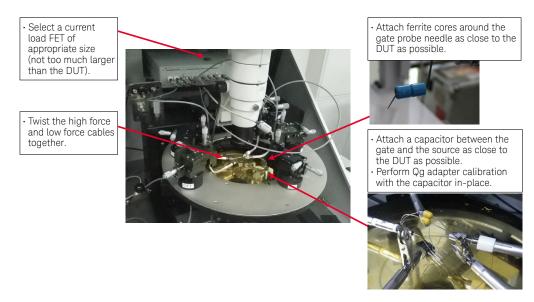

| On-wafer gate charge measurement                                     |     |

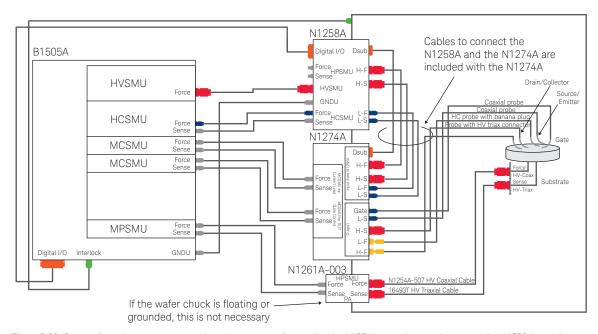

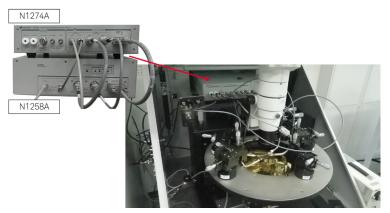

| On-Wafer Gate Charge Measurement using the HCSMU (B1512A)            |     |

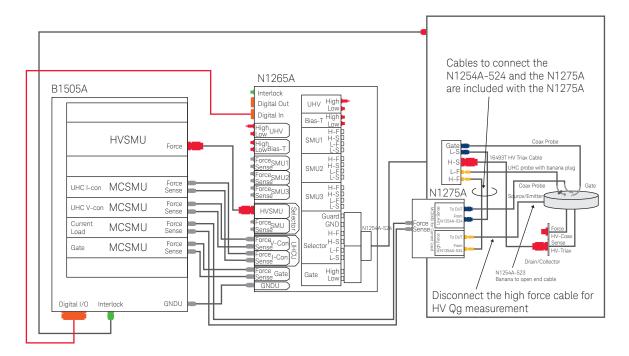

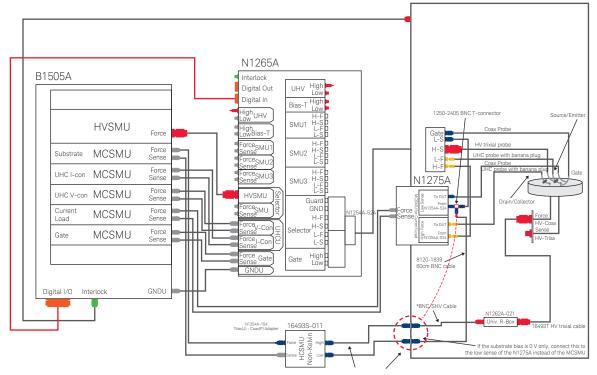

| On-Wafer Gate Charge Measurement using the UHCU (N1265A)             |     |

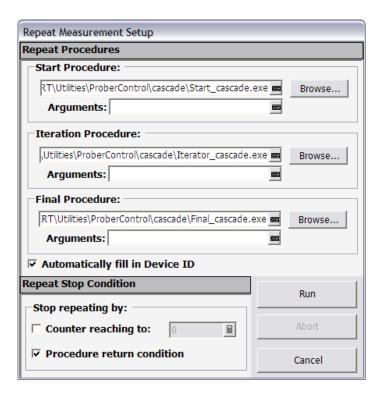

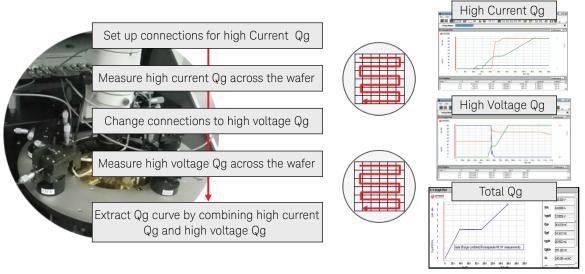

| Automating On-Wafer Gate Charge Measurement                          |     |

| Appendix A – Keysight Technologies' Parametric Measurement Solutions |     |

| Semiconductor Parameter/Device Analyzers                             |     |

| Power Device Analyzers/Curve Tracers                                 |     |

| Modular Source/Monitor Units                                         |     |

| Benchtop Source/Measure Units                                        |     |

| Switching Matrices                                                   |     |

| Impedance Analyzers                                                  |     |

| Glossary                                                             |     |

| About the Author                                                     | 271 |

### Preface

"An expert is a man who has made all the mistakes, which can be made, in a very narrow field" – Niels Bohr

It has been seven years since we published the first edition of this handbook, and in the interim many things have changed. Fully recovered from the shock (in 1999) of transitioning from Hewlett-Packard to Agilent Technologies, in 2014 we once again changed names as the electronic test and measurement portion of Agilent became Keysight Technologies ("unlocking measurement insights"). Despite our two name changes, Keysight remains true to its roots as HP's original business. We continue to work at supplying our customers with the best electronic test solutions available.

If you have an earlier version of this handbook, then you probably want to know: What is new? The main thing you will notice about this edition versus earlier ones is the addition of any entire new chapter (chapter 9) devoted to power device test. This was necessary as Keysight has come out with many new solutions to test power devices since the handbook was first published. Also, power device testing is a complex enough task that it warrants having a chapter devoted exclusively to it. The other changes have been interwoven into existing chapters, and they include updated information on enhancements to existing products as well as information on some of our newer products.

Many people helped with the content and review of this updated handbook, but in particular I would like to acknowledge the contributions of Yasushi Okawa for his many excellent presentations and training materials on power device test. Without those <a href="chapter9">chapter 9</a> would have been much more difficult to write. Also, thanks go to Helen Amato, Biow-Huei Sim and Gwen Soo for their extensive work to update the handbook layout and images. Overall I think that there is enough new content in this edition to enable engineers and researchers to make accurate parametric measurements on low and high power devices both now and for many years into the future.

Alan Wadsworth January 2018

# Chapter 1

# Keysight Technologies' Parametric Measurement Solutions

"The central activity of engineering, as distinguished from science, is the design of new devices, processes and systems." — Myron Tribus

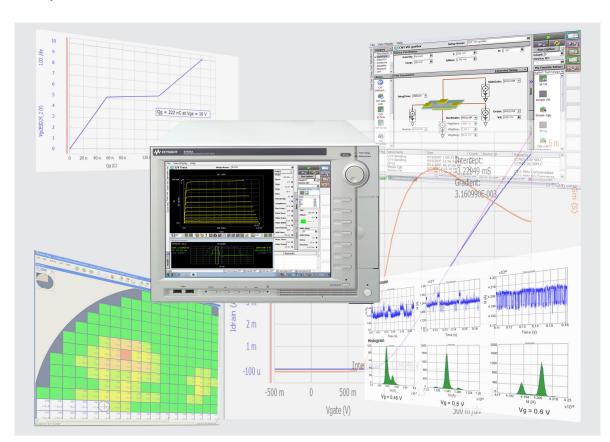

### What is a parametric test?

The question as to what constitutes parametric testing is an interesting one and is possibly open to some debate. Nevertheless, in general parametric testing involves the electrical testing and characterization of four main types of semiconductor devices: resistors, diodes, transistors, and capacitors. This is not to say that parametric tests never involve the testing of other device types; however, the vast majority of parametric test structures can be classified into one of these categories or considered to be a combination of these categories.

Figure 1.1. Parametric tests involve the testing of these four basic device types.

The vast majority of parametric testing involves either current versus voltage (IV) or capacitance versus voltage (CV) measurements.

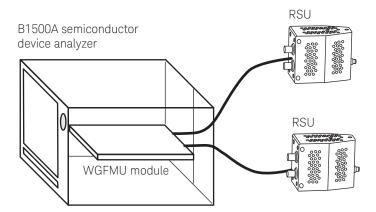

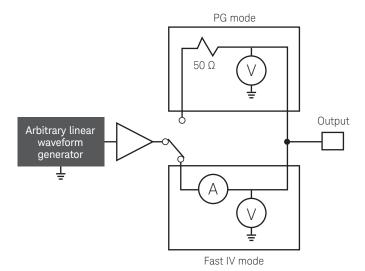

To many people, parametric testing means "DC" testing, but this is not an accurate description. Of course, it can take source/monitor units (SMUs) anywhere from milliseconds to seconds to make a measurement, which is certainly "slow" by the standards of functional testers (which typically perform measurements in the nanosecond or picosecond range). However, in recent years, the need to perform extremely fast parametric measurements (1 µs spot measurements with data sampling rates in the nanosecond range) has greatly increased. This has required the creation of new measurement module types (such as the waveform generator/fast measurement unit or WGFMU) to meet this need. Extremely fast IV and pulsed IV measurements will continue to take on increased importance in the future, as transistor lithographies continue to shrink and more exotic materials are incorporated into semiconductor processes.

### What is a parametric test? (continued)

One major subcategory of parametric testing is reliability testing. Reliability testing relies heavily upon the well-known Arrhenius equation that expresses the rate constant (k) of a chemical reaction as follows:

$$k=Ae^{-\frac{E_a}{RT}}$$

Where:

A is the pre-exponential factor E<sub>a</sub> is the activation energy R is the ideal gas constant T is the temperature in degree Kelvin

In reliability testing, devices are typically stressed by the application of large currents and/or voltages (larger than that experienced by the devices under normal operation) to lower the value of the activation energy and thereby increase the rate of the failure mechanism. Temperature is also often increased to achieve this same purpose. Once the failure mechanism occurs, then the expected failure rate under normal operating conditions can then be extrapolated using a variety of mathematical and statistical techniques.

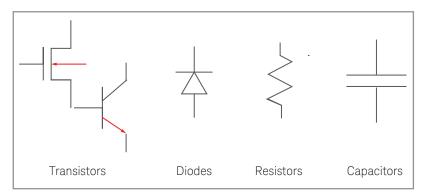

### Why is parametric testing performed?

The purpose of parametric testing is to determine the characteristics of a semiconductor manufacturing process. Broadly speaking, parametric testing covers three main areas: process development, device modeling, and process control.

Figure 1.2. Parametric testing is widely used in three main areas: process development, device modeling, and process control.

### Why is parametric testing performed? (continued)

The first two of these areas are performed in a laboratory, R&D or pre-production environment, while the last one is performed in a manufacturing environment. The parametric equipment used in these disparate environments obviously has different requirements, with benchtop instruments being used for process development and process modeling, and high-throughput testers being used for process production.

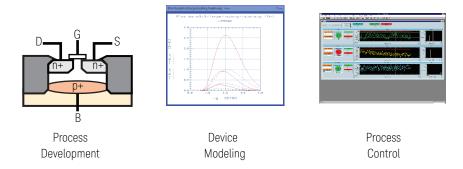

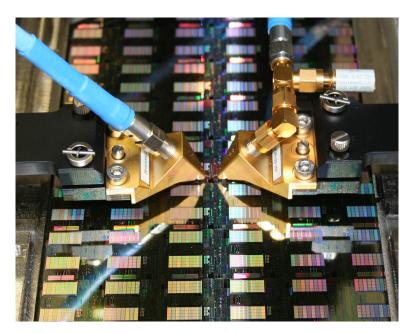

Figure 1.3. A production parametric tester is designed to optimize throughput

It is important to understand that parametric test is, almost never performed on final products. Instead it is performed on special structures that are designed to yield information about the process itself. Parametric tests are also generally performed directly on semiconductor wafers. In production test, the parametric test structures are sometimes located in the scribe lanes or "streets" of the wafer to minimize the wafer area taken up by these devices. However, for process development and reliability testing entire wafers of nothing but parametric test structures are often fabricated.

Figure 1.4. To conserve valuable wafer area, parametric test structures are sometimes placed in the wafer's scribe lines (or "streets").

### Where is parametric testing done?

In production, parametric tests are typically performed on wafers after they have completed the wafer fabrication process (i.e. after passivation has been applied) but before electrical sort (E-sort) on the functional product dice.

Figure 1.5. Parametric testing is performed after wafer fabrication is complete but before functional product verification.

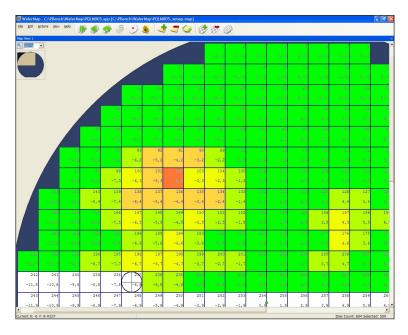

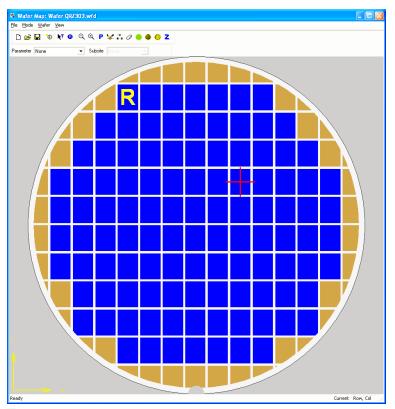

Each wafer from every lot is tested and the data is stored into a database. As the amount of data is quite massive, various software tools are employed to manipulate the data into a variety of different formats. One popular format is the wafer map, where a scalar quantity is plotted across a wafer using different colors for different ranges of the data value.

Figure 1.6. Wafer map example.

### Where is parametric testing done? (continued)

For advanced processes, conventional test structures placed in the scribe lines or even drop-in test die placed around the wafer may not be sufficient to adequately characterize the process. Advanced processes typically require much more testing due to their innate complexity, and it is sometimes difficult to fit all of the necessary test structures into the available area. Unfortunately, the tips of the probe card have physical limitations on how small they can be made and still maintain reasonable probe card lifetimes, which in turn creates physical limits on the minimum size of the probe pads. This means that the pads cannot be physically scaled down as devices scale down with each new process generation.

Figure 1.7. Pad sizes cannot be scaled down with changing design rules, which limit the number of conventional test structures that can be placed on a wafer.

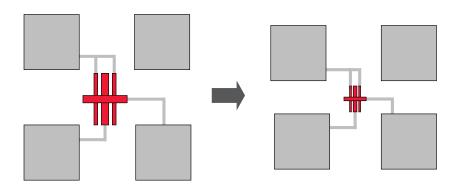

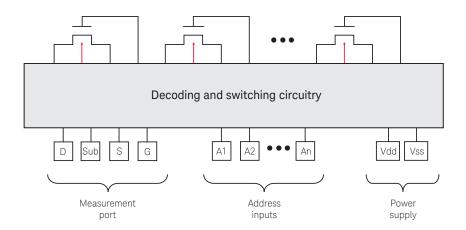

One solution to this issue is to use arrays, since an array allows test devices to share pads and thereby improve the test device to pad ratio. An example of this scheme is shown below.

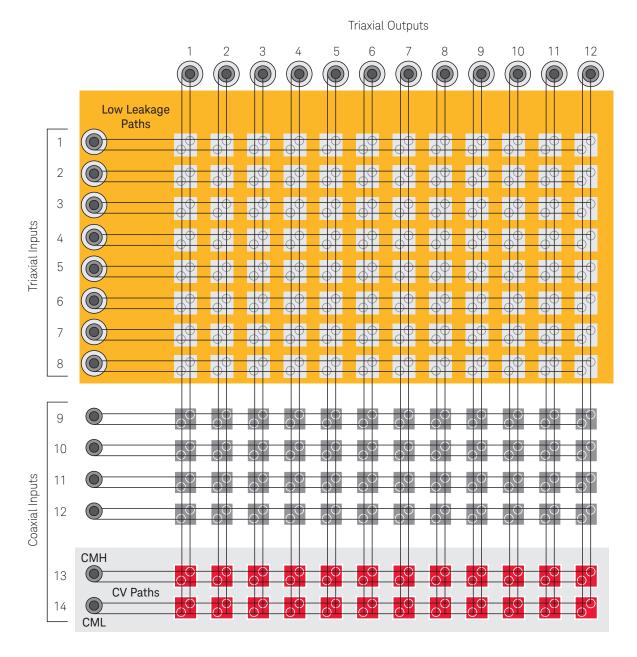

Figure 1.8. An example of an addressable array scheme used for production parametric testing.

Addressable arrays can offer significant throughput improvement over conventional test device arrangements, although achieving substantial test time reduction requires a complete re-engineering of all of the parametric test processes.

### Parametric instrument history

The first instruments that could perform anything resembling parametric measurement were analog curve tracers. However, these instruments had a number of limitations, not the least of which was that the "data" was a display on a CRT screen. The only way to save this data was to take a Polaroid picture of the display, which still did not supply you with actual numeric information.

### The 1980's

In the early 1980's, Keysight Technologies (then part of Hewlett Packard) introduced the world's first digital parameter analyzer, the 4145A. The 4145A was the first instrument to incorporate four source/monitor units (to be discussed further in <a href="chapter3">chapter 3</a>) in a single box along with the software necessary to integrate all of these resources. The 4145A produced plots similar to that of a curve tracer, but its output consisted of discrete points of digital data that could be transferred into other software for storage and analysis. This product was something revolutionary for the semiconductor industry, and the 4145A quickly supplanted the curve tracer except for a few specialized applications. Later in the 1980's, an improved version of this product, the 4145B, was also introduced.

Figure 1.9. The 4145B Semiconductor Parameter Analyzer

### The 1990's

In the early 1990's, Keysight Technologies (then part of Hewlett Packard) introduced the 4155 and 4156 semi-conductor parameter analyzers. These instruments built upon the 4145A/B by adding new capabilities including a color display and keyboard, automatic data analysis capability, a pulsed sweep capability, a thinned-out sampling mode, DC and AC stressing and a standby mode, just to name a few. There were several versions of these products (the "A", "B" and "C" models), and with each subsequent version more features and capabilities were added. In particular, quasi-static capacitance versus voltage (QSCV) measurement capability was added to the "C" version along with vastly improved voltage monitor unit (VMU) measurement capability.

Figure 1.10. The 4156C Precision Semiconductor Parameter Analyzer

### The 21st century

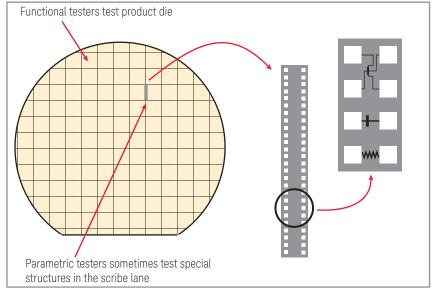

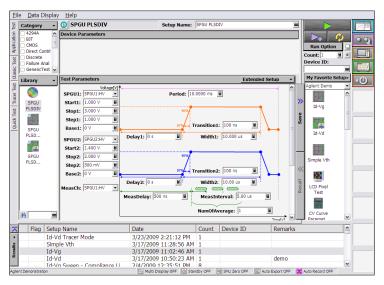

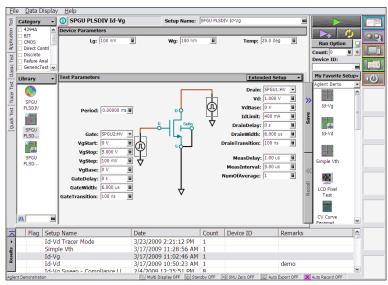

At the beginning of the 21st century, it became increasingly clear that parametric testing was becoming more complicated and that a complete solution needed to be able to perform more than just IV measurements. A solution that could perform both CV and IV measurements was required, and this solution also had to have the flexibility to add additional measurement resources in the future as testing needs evolved. To meet these challenges, Keysight Technologies (then part of Agilent Technologies) introduced the B1500A semiconductor device analyzer with Keysight EasyEXPERT software in 2005. The B1500A supports all aspects of parametric testing, from basic manual measurements to test automation across a wafer in conjunction with a semiautomatic wafer prober. Because the B1500A utilizes the Microsoft® Windows® operating system, it integrates easily into PC-based work environments. In addition, the familiar Windows graphical user interface (GUI) and convenient online help menus minimize the need for instrument training. The B1500A has already supplanted the 4155C and 4156C as the tool of choice for state-of-the-art parametric measurement needs.

Figure 1.11. The B1500A Semiconductor Device Analyzer

The B1500A is a modular instrument, and it supports a variety of module types. Modularity is an extremely important feature since parametric testing continues to be an extremely dynamic area where new types of testing are constantly being required. Parametric testing requires more than simple source/monitor unit resources, and increasingly complex tests requiring capacitance testing, high-speed testing and fast pulsed measurement are becoming common. Modularity ensures that measurement equipment does not become outdated and that you have the flexibility of adding new test capabilities to your parametric measurement equipment as your measurement needs change in the future.

### The 21st century (continued)

Figure 1.12. The ten-slot B1500A supports a variety of types of source/monitor units as well as a capacitance measurement module, a high-voltage pulse generator module and a waveform generator/fast measurement unit module.

In addition to the B1500A, Keysight introduced the B2900A family of precision benchtop SMUs. The B2900A SMU family has an integrated GUI that supports measurement and graphing right from the front panel, and it is available in both one and two channel versions.

|                            | B2901A                       | B2902A | B2911A | B2912A |

|----------------------------|------------------------------|--------|--------|--------|

| Number of Channels         | 1                            | 2      | 1      | 2      |

| Maximum V                  | ±210 V                       |        |        |        |

| Maximum I (DC/Pulsed)      | ±3 A (DC) / ±10.5 A (Pulsed) |        |        |        |

| Minimum Pulse Width        | 50 μs                        |        |        |        |

| Measurement Resolution (I) | 100 fA 10 fA                 |        | fA     |        |

| Measurement Resolution (V) | 100 nV 100 nV                |        | ) nV   |        |

| Minimum Sampling Interval  | 20 μs 10 μs                  |        | μs     |        |

Figure 1.13. Table showing key measurement capabilities of the B2900A benchtop SMU series.

The B2900A SMUs are supported in a variety of different software platforms (including BenchVue), but for parametric test, the key feature is that they are supported in EasyEXPERT group+. In fact, Keysight can supply a cable (N1294A-032 Digital I/O Trigger Cable for Multiple Unit Control) that allows you to control up to four two-channel B2900A SMUs (eight SMU channels) and maintain complete synchronization between all eight channels. If you require only basic IV measurements functions, it is very cost effective to use one or more B2900A SMUs with EasyEXPERT group+. Also, the B2900A SMUs can supply more current and voltage than B1500A SMUs can. Thus they can provide a good intermediate solution between the B1500A and the B1505A and B1506A (which will be discussed next).

Figure 1.14. B2902A two-channel SMU being controlled with EasyEXPERT group+ software using an external PC.

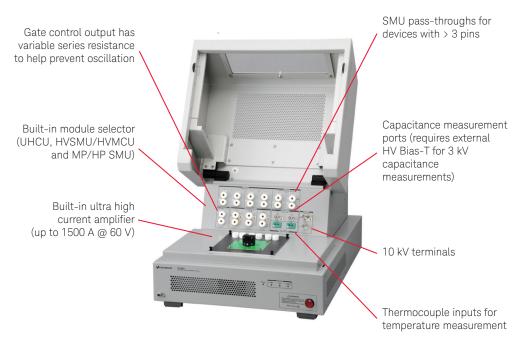

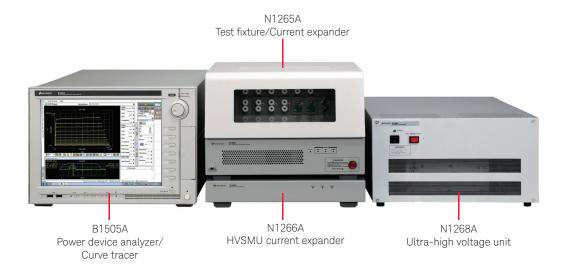

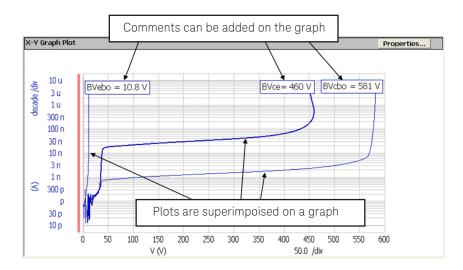

To meet the needs of the expanding high-power market and to supply an alternative to conventional analog curve tracers (which are no longer being made by major manufacturers), Keysight introduced the B1505A Power Device Analyzer/Curve Tracer in 2009. The B1505A can supply up to  $\pm 1500$  A and  $\pm 10$  kV, and it can perform 10  $\mu$ s pulsed measurements. In addition, the B1505A comes with a tracer test mode that supports a knob sweep capability and an oscilloscope view that enables you to verify current and voltage pulses. The B1505A also supports automated CV measurements at up to 3 kV of DC bias, and gate charge measurements at up to 1100 A and 3 kV.

Figure 1.15. The B1505A power device analyzer/curve tracer with its ultra-high current and ultra-high voltage modules.

Unlike analog curve tracers, the B1505A is PC-based and uses the same user-friendly Keysight EasyEXPERT software as the B1500A.

Several new features in the B1505A's tracer test mode provide dramatic usability improvements over traditional curve tracers. A snapshot feature allows you to save and display multiple data traces so that you can easily compare them with data from the current measurement. A stoplight feature allows you to graphically define forbidden regions (either voltage or current based) such that the measurement immediately ceases if the trace enters the forbidden area. Best of all, an auto-record feature keeps a running record of the most recent trace changes so that you can replay and save measurement trace data even if the device is inadvertently damaged or destroyed. Taken together, these improvements represent a truly revolutionary advancement in curve tracer design that can significantly reduce device characterization cycle times.

A sister product to the B1505A is the B1506A Power Device Analyzer for Circuit Design. The B1506A has many of the same capabilities as does the B1505A, but it is focused on the needs of power semiconductor device users and circuit designers rather than on the needs of power device manufacturers. The B1506A can supply up to  $\pm 1500$  A and  $\pm 3$  kV, and it can make 10  $\mu$ s pulsed measurements. Just like the B1505A, the B1506A supports automated CV measurements at up to 3 kV of DC bias and gate charge measurements at up to 1100 A and 3 kV. However, the B1506A does not support on-wafer CV or gate charge measurements, the 10 kV expander unit, or the GaN current collapse switch.

Figure 1.16. The B1506A power device analyzer for circuit design.

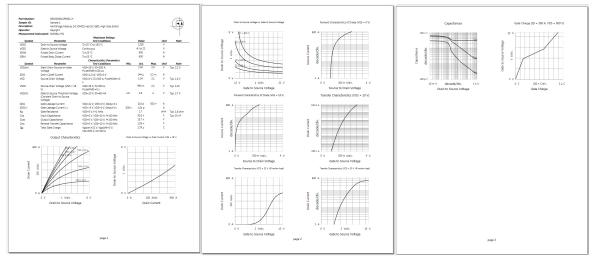

The B1506A also has its own unique software interface, Easy Test Navigator (although it also supports EasyEX-PERT group+). For engineers who are not test experts and whose only goal is to create a device data sheet, Easy Test Navigator provides an intuitive interface that can automatically generate a complete device data sheet.

Figure 1.17. Easy Test Navigator can automatically generate a customized datasheet.

Power device performance is inextricably tied-in to package thermal performance, so the ability to measure device operation across different temperatures is extremely important. For this reason, both the B1505A and B1506A support packaged device thermal testing. If you only need to characterize device performance at room and hot temperature, then a thermal plate option is available (sold by inTEST Thermal Solutions). The thermal plate temperature is controllable via both EasyEXPERT group+ and Easy Test Navigator software, and the N1265A and B1506A test fixtures come with two k-type thermocouple inputs so that both the ambient and DUT temperature can be monitored at the same time.

Figure 1.18. The B1505A/B1506A thermal plate can support temperature measurements from room temperature up to 250°C.

If both cold and hot temperature measurements are necessary, then Keysight can supply thermal test adapters for both the N1265A and B1506A test fixtures that support the use of inTEST temperature forcing systems.

Figure 1.19. The B1505A/B1506A can support the use of inTEST temperature forcing systems for temperature measurements from -50°C to 250°C.

Both EasyEXPERT and Easy Test Navigator software can support temperature triggered measurements (using measured data from the thermocouple inputs). This allows for the automated measurement of device parameters across temperature.

# Chapter 2 Parametric Measurement Basics

"I often say that when you can measure what you are speaking about, and express it in numbers, you know something about it ..."

"But when you cannot measure it, when you cannot express it in numbers, your knowledge is of a meager and unsatisfactory kind; it may be the beginning of knowledge, but you have scarcely, in your thoughts, advanced to the stage of science, whatever the matter may be."

- William Thomson (Lord Kelvin)

### Measurement terminology

Before you can begin to collect measurement data, you need to know some basic measurement terminology. In particular, understanding the precise meaning of the terms accuracy, repeatability and resolution is essential to understanding parametric test and the measurement capabilities of a parametric measurement resource.

### Accuracy and repeatability

Accuracy and repeatability are related but different. Accuracy is the degree of conformity of a measured or calculated quantity to its actual (true) value. Repeatability (also known as precision) is the degree to which repeated measurements or calculations show the same or similar results. Accuracy and repeatability do not have any innate correlation. A measurement can have high accuracy and high repeatability, high accuracy and low repeatability, low accuracy and high repeatability, or both low accuracy and low repeatability.

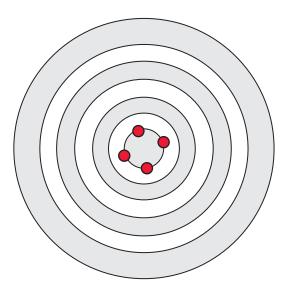

The visual analogy that is often used to explain these terms is a bull's-eye target. A group of points that are close to the center of a target but spaced far apart from one another (as shown below) have high accuracy but low repeatability.

High accuracy, low repeatability

Figure 2.1. High accuracy and low repeatability.

### Accuracy and repeatability (continued)

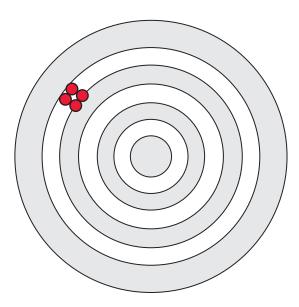

A group of points that are far from the center of a target but spaced close together (as shown below) have low accuracy but high repeatability.

Low accuracy, high repeatability

Figure 2.2. Low accuracy and high repeatability.

The analogies for the two other cases should be fairly obvious. For production parametric test, repeatability is usually more important than absolute accuracy. This is because parametric testing is concerned with monitoring trends, which makes having highly repeatable measurements extremely important.

### Resolution

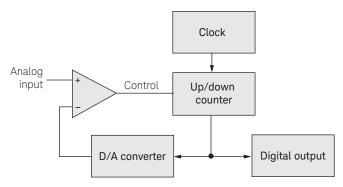

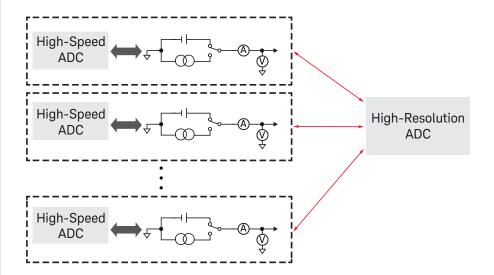

In a parametric test, resolution is what allows us to gauge accuracy and repeatability. In this sense, it is the most important specification for parametric testing. Resolution is the smallest change in data that an instrument can display. The easiest way to think about this is in terms of an analog-to-digital converter (ADC) circuit. The figure below shows a simplified version of an ADC:

Figure 2.3. Simplified analog-to-digital converter (ADC) circuit.

### Resolution (continued)

As this illustrates, the number of bits available to the digital-to-analog converter (DAC) will determine the fineness of the measurement detail that can be distinguished, which is the resolution. For example, a resolution of 20 bits represents the ability to distinguish one part in  $2^{20}$  or 1,048,576 (basically one part in a million).

To express the measurement resolution in terms of current or voltage, you need to know the measurement range in which you are operating. For example, in a 5 V measurement range, the ADC measures from -5 V to +5 V, which (assuming a 20-bit ADC) yields a readable or resolvable measurement resolution of:

$$\frac{(5+5)V}{1,048,576} \approx 10 \text{ }\mu\text{V}$$

However, due to noise and other factors, the readable resolution is not the same as the resolution specified in a data sheet. The resolution specified in a data sheet takes into account factors such as thermal noise and amplifier offset and noise, which introduce a stochastic element into the data sheet specification. Typically, the specified resolution is 1 to 2 orders of magnitude larger than the readable resolution.

### Traceability

Traceability is defined as the property of the result of a measurement or the value of a standard whereby it can be related to stated references, usually national or international standards, through an unbroken chain of comparisons, all having stated uncertainties. It is important for any company that is manufacturing measurement equipment to establish traceability up to national and international standards, in order to guarantee that measurements are being made correctly.

There are a number of National Metrology Institutes (NMIs) that provide standard reference materials of the highest quality and metrological value. The intent of all NMIs is to realize SI units (such as volts, amperes, ohms, etc.) as closely as possible. A partial list of NMIs is shown below.

| Name                                           | Acronym | Country |

|------------------------------------------------|---------|---------|

| National Institute of Standards and Technology | NIST    | USA     |

| National Metrology Institute of Japan          | NMIJ    | Japan   |

| National Physical Laboratory                   | NPL     | UK      |

| Physikalisch Technische Bundesanstalt          | PTB     | Germany |

Keysight Technologies obtains standards from these NMIs to use as calibration references. Keysight's measurement products include a certificate of calibration when they are originally shipped from the factory or after a product calibration has been performed. This document is in compliance with the traceability requirements from these NMIs.

### Shielding and guarding

Beginners sometimes confuse shielding with guarding, although they are quite different and have totally different purposes. The purpose of shielding is to prevent electrostatic noise from interfering with a measurement, while the purpose of guarding is to prevent leakage of currents and enable low-current measurements (in the femtoamp range). A shield does not act as a guard, and a guard does not necessarily provide good shielding. As a general rule of thumb, when making measurements below 1 nanoamp (10<sup>-9</sup> A) you should use guarding; when making measurements below 1 picoamp (10<sup>-12</sup> A) you should use both guarding and shielding.

### Shielding: Maintaining a low noise floor

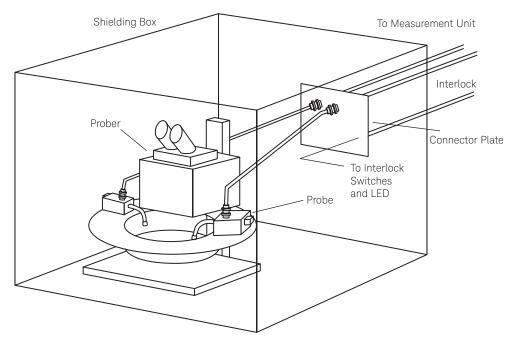

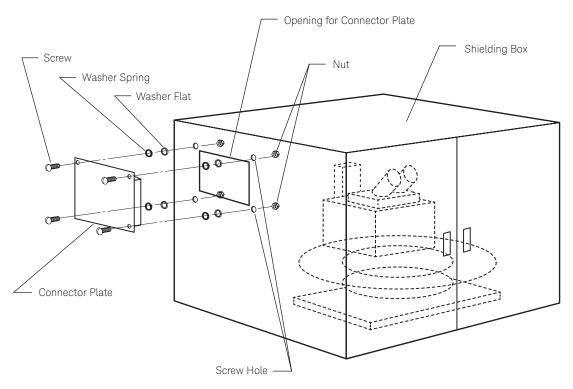

Shielding involves surrounding the measurement environment with conductive material so as to eliminate electrostatic noise. Basic electromagnetic field theory shows that surrounding a volume with conductive material creates a barrier across which electromagnetic signals cannot cross. This is also often referred to as creating a "Faraday cage." Typically, for parametric tests, this is accomplished using some sort of shielding box as shown below:

Figure 2.4. A well-shielded parametric measurement environment.

There are a number of best practices that one should keep in mind when trying to create a well-shielded measurement environment:

- Enclose the measurement area with conductive material and measurement cables with a metal shield or braid

- Electrically connect shielding enclosure and cable shields to the test instrument common (shield) and/or to earth ground.

- To reduce capacitance and vibration effects, keep the shielding and test circuit as far apart as possible.

- Eliminate "light leaks" through gaps around doors and hinges, tubing and cable entry points, connectors and connector panels, and seams/joints between panels.

- Fill seams/gaps/joints with conductive caulking or gaskets.

### Shielding: Maintaining a low noise floor (continued)

A reasonable question to ask is: Since a proper shield completely surrounds the measurement environment, how do you connect anything to it? The solution is to use a connector plate that is specifically designed for this purpose.

Figure 2.5. Using a connector plate to connect through a shielding box.

Keysight Technologies can supply a variety of connector plates with both triaxial and BNC connectors specifically for this purpose.

In summary, the following are the key points to keep in mind when constructing a well-shielded measurement environment:

- Keep all charged objects (including people) and conductors away from the measurement area.

- Use highly conductive materials instead of insulating materials near the test circuit.

- Avoid movement and vibration near the measurement area (air currents can cause movement and/or vibration).

- When measuring currents <1 pA, shield the measurement area with a conductive (metal) enclosure and connect the enclosure to the test instrument common (shield) and/or to earth ground.

- Minimize the capacitance between the shielding enclosure and the test circuit.

### Avoiding ground loops

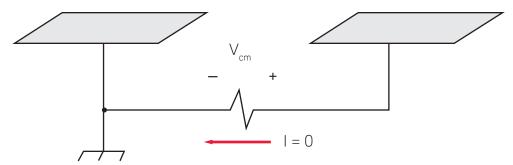

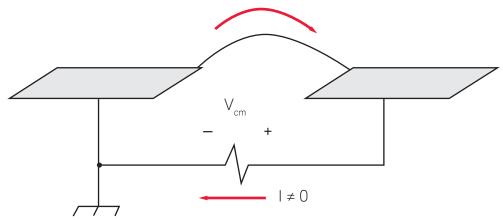

One common problem when using shields that has not yet been mentioned is creating ground loops. If all shields are tied to ground and you have multiple shielded instruments and cables in a given measurement environment, then it is almost a certainty that the grounds to which these are tied are not at the same potential. Consider the simple case of two conductive planes both tied to ground:

Figure 2.6. Conductive planes connected at only one point cannot have any current flow between them.

As long as these conductive planes are only connected together at one point, any difference in the common mode voltage ( $V_{cm}$ ) of these planes is not an issue because no current can flow between the planes. However, if the ground planes are strapped together in more than one location then a loop path for current is created that can cause significant current to flow through the conductive planes. This common mode voltage can seriously impact parametric measurement results:

Figure 2.7. Conductive planes connected at multiple points creates a loop for current (a condition to be avoided).

Thus, although it may be counter-intuitive, the best strategy when making parametric measurements is to avoid excessive ground connections and instead connect everything together through a single ground point.

Note: Since instruments almost always have their ground tied to chassis ground, which is in turn tied to earth ground, this is already taken care of for you. If you suspect that you are having a grounding issue, then the simplest solution is to make sure that the power cords of all of your equipment are tied together to a common power strip.

### Guarding: Isolation for low-current measurement

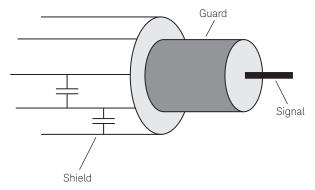

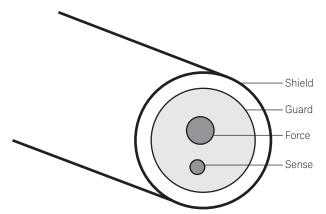

Guarding involves surrounding a signal line with an actively driven conductor maintained at the same voltage potential as that of the signal to eliminate leakage currents. Good guarding can only be achieved using triaxial connectors and cabling. In a triaxial cable, the signal line is surrounded by the guard line (separated of course by insulating material), which is in turn surrounded by a grounded shield line (also separated by insulating material). The following illustration shows a cut-away view of a triaxial cable.

Figure 2.8. Cut-away view of a triaxial cable, showing parasitic capacitance between shield to guard and guard to signal.

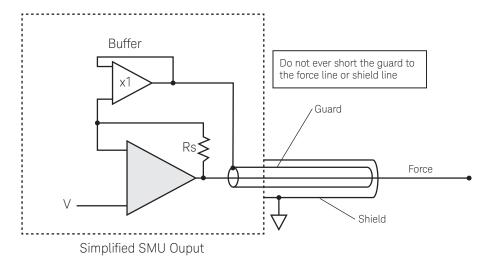

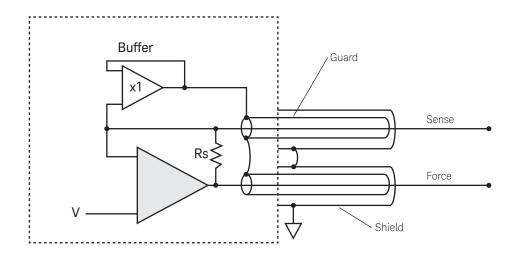

Even though there is parasitic capacitance in this cable, the driven guard effectively eliminates the effects of this parasitic capacitance by isolating the signal line from the shield. The diagram below shows the structure of the circuitry driving the guarded (triaxial) output.

Figure 2.9. Circuitry to provide a guarded (triaxial) output.

The guard line is actively driven by a buffer circuit to maintain the same voltage potential as the center conductor (force) line. Obviously, if you short the guard line to either the force or shield lines then you risk damaging the output circuitry.

### Guarding: Isolation for low-current measurement (continued)

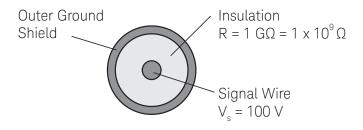

The inevitable question gets asked: Why do we need triaxial cables to measure low currents? After all, BNC cables use insulating material, so why should we expect any leakage current? Some simple calculations help to illustrate the need for triaxial cables when measuring ultra-low currents. Assume that the insulation material has a resistance of 1  $G\Omega$  and that we apply 100 V to the center conductor:

Figure 2.10. Leakage current when using a BNC (coaxial) cable.

A simple calculation shows that the leakage current will be:

$$i_{leak} = \frac{100 \text{ V}}{1 \times 10^9 \,\Omega} = 1 \times 10^{-7} \text{ A} = 100 \text{ nA}$$

Obviously, if we are trying to measure currents in the femtoamp  $(10^{-15} \text{ A})$  current range, we cannot use cables with 100 nA of leakage current.

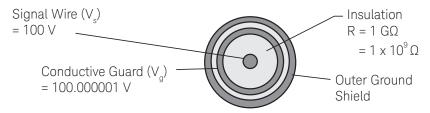

Now let us examine the same case using a triaxial cable. In this case we assume that the driven guard can track the applied (signal) voltage to within one part in a million (which is a reasonable and conservative assumption):

Figure 2.11. Leakage current when using a triaxial cable.

Thus, the leakage current will be the difference between the voltages of the signal and guard divided by the effective resistance:

$$i_{l_{eak}} = \frac{\left(100,000001 \, V - 100 \, V\right)}{1 \times 10^{9} \, \Omega} = \frac{1 \times 10^{-6} \, V}{1 \times 10^{9} \, \Omega} = 1 \times 10^{-15} \, A = 1 \, fA$$

By using triaxial cables with a driven guard, we have reduced the leakage current to 1 fA, or by a factor of one-hundred million (10°) as compared to using a BNC cable. It is for this reason that all low-current parametric measurements are made using triaxial cables.

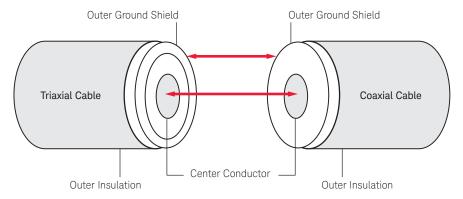

### Connecting triaxial and BNC cables

Inevitably, you will be faced with the issue of connecting BNC and triaxial cables. The three key questions that require answers are:

- 1. How do I connect up the driven guard?

- 2. How does this affect my low-current measurement capability?

- 3. Where do I get the necessary connectors?

We will address each of these concerns in turn.

The most important point to understand when connecting up triaxial and BNC connectors is how to connect the driven guard. Remember that the driven guard exists to allow for sub-nanoamp measurements. We can state as a general rule of thumb that for current measurements above one nanoamp, we can simply connect the force/sense line to the center conductor of the BNC cable and the shield to the outer ground shield of the BNC cable as shown below.

Figure 2.12. Triaxial to BNC connection when not making low-current measurements (1 nA and above).

The advantage of this configuration is its simplicity. We do not need to take any special precautions with the driven guard.

However, the only way that we can make a low-current (below one nanoamp) measurement with a BNC cable is to connect the driven guard to the outer shield of the BNC cable as shown below.

Figure 2.13. Triaxial to BNC connection when making low-current measurements.

### Connecting triaxial and BNC cables (continued)

This configuration presents a couple of significant challenges:

- 1. The outer shield of the BNC must be isolated from ground.

- 2. The outer shield of the BNC can reach dangerous voltages (>40 V), therefore precautions must be taken to ensure that the user is protected from receiving a fatal electrical shock.

There are analytical wafer prober companies with ready-made solutions to isolate the BNC shield from ground to prevent these types of issues from occurring.

You must be very careful when selecting triaxial to BNC adapters to make sure that you understand which of the above two schemes the adapter is using. If you are uncertain about your connector, then it is strongly advised that you use a multi-meter to check the connections. You can purchase triaxial to BNC connectors from Keysight as well as a variety of third-party suppliers.

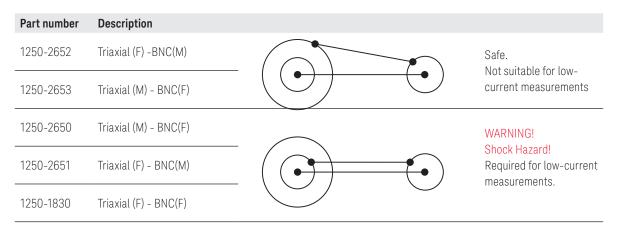

Figure 2.14. Table showing the different types of triaxial to BNC connectors supplied by Keysight Technologies.

### Kelvin (4-wire) measurements

No wire or cable is a perfect conductor. Everything that you use to connect your instruments to the device under test (DUT) has some innate resistance (even though the resistance may be very small). The important question is: When do I need to be concerned about this cable resistance? The corollary to this question is: How do I eliminate the cable resistance effects? In this section, we will answer both of these questions.

Every cable can be thought of as a resistor. The resistance of a cable or wire typically used in parametric tests is very small (on the order of milliohms). Obviously, if you are trying to measure a test structure with a resistance that is many orders of magnitude greater than 0.1  $\Omega$ , you can safely ignore the cable resistance effects. However, suppose you are trying to measure a structure with only a few Ohms of resistance. In this case, the error introduced by the cable resistance can significantly skew your measurement results.

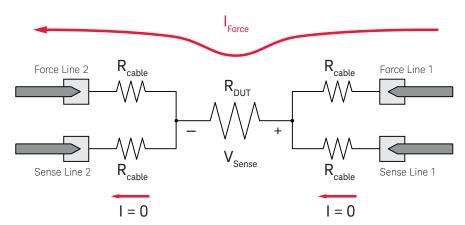

In order to remove the effects of the cable resistance, we need to eliminate the resistive voltage drop caused by the current flow through the cable and only measure the resistive effects associated with the test structure. We can do this by making what is known as a 4-wire measurement. This technique requires two separate lines for each terminal on the structure that we want to measure. One pair of lines is used to force current to the DUT, and the other pair of lines is used to sense the voltage measurement. The key point of this measurement is that we separate out the lines used to supply current to the DUT from the lines used to measure the voltage drop across the device. Since the sense lines making the voltage measurement are not conducting any current, there is no voltage drop due to cable resistance. Therefore, the cable resistance effects are eliminated. This technique is often described as a Kelvin measurement, after the famous British mathematician and physicist Lord Kelvin who invented the technique (and who is quoted at the beginning of this chapter).

### Kelvin (4-wire) measurements (continued)

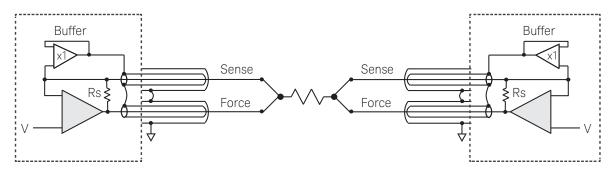

Figure 2.15. A Kelvin (or 4-wire) voltage measurement eliminates the effects of cable resistance by separating out the lines carrying the force current from the lines sensing the voltage.

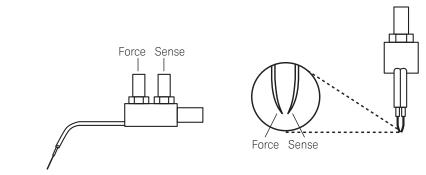

To be effective, a Kelvin measurement requires that the force and sense lines be shorted together as close to the DUT as possible. Many analytical wafer probing companies make Kelvin triaxial positioners that short the force and sense lines together right at the test pad.

Figure 2.16. Kelvin triaxial positioners (shown above) are ideal since they terminate the force and sense lines at the DUT pad.

### Kelvin triaxial cables

Keysight Technologies can supply Kelvin triaxial cables. Each Kelvin triaxial cable can replace two standard triaxial cables. The internal configuration of the Kelvin triaxial cable is as shown below:

Figure 2.17. The Kelvin triaxial cable combines both the force and sense lines into a single cable.

The Kelvin triaxial cable generally provides better low-noise performance than using two standard triaxial cables. In addition, the connector on the Kelvin triaxial cable makes it impossible to connect the force and sense lines incorrectly.

Note: You should only order this cable if you are certain that whatever equipment you plan on using it with (wafer prober, switching matrix, etc.) supports this connector.

Figure 2.18. The Kelvin triaxial cable mates with Keysight SMUs and many analytical wafer prober connector plates.

### Noise in electrical measurements

Noise is an inescapable part of electrical measurement that arises from the fact that all electronic charge is discrete. It is impossible to give adequate coverage to all of the possible types of noise that can be encountered in parametric testing in this short section. Instead, we will give a brief overview of the most common types of electrical noise.

### Shot noise

Shot noise is the noise associated with electrical current. It is the result of the fact that an electrical current consists of a flow of electrons and that the electrons have a discrete charge. The value that we define as the electrical current is the average value of the number of electrons passing through a given cross section per second. This is given by:

$$l = nq$$

Where q is the value of the electron charge and n is the average number of electrons passing through the given cross section per unit time. The true current, i(t), is time dependent and fluctuates around this average value depending upon the actual number of electrons passing over the given cross section at any instant in time. The shot noise can therefore be written as:

$$i_{shot}(t) = i(t) - i = i(t) - nq$$

By making certain idealized assumptions, we can show that the spectral density function of the shot noise is proportional only to the electronic charge and the value of the average current:

$$S_i(f) \alpha ql$$

The most important feature of this function is that the noise spectrum is constant at all frequencies. Spectra with this type of frequency independence are referred to as white noise. Shot noise can have a particularly strong impact on parametric measurements when you are trying to measure a very small signal in a DUT that is being biased by a much larger DC current.

It should be pointed out that the above results are only an approximation. In reality, one can easily see that the spectral density function cannot have a constant value across all frequencies. If we were to calculate the mean square current by integrating the spectral density function across all frequencies (from zero to infinity), then we would end up with an infinite value. This does not make any physical sense, since no real current can supply an infinite noise power. There has to be an upper frequency limit at which the spectral density function drops off. However, for most situation of interest in parametric tests, this frequency is so high that we can make the simplifying assumption that shot noise is constant across frequency.

### Thermal noise

Resistors that are not carrying any current can exhibit voltage fluctuations due to the random thermal motion of electrons. This thermal noise (also known as Johnson noise) results in voltage fluctuations that have a zero time average value and a spectral density function described by the equation shown below:

$$S_{y}(f) = 4kTR$$

In this equation, k is the Boltzmann's constant, T is the temperature in degree Kelvin and R is the resistance. Since this spectral density function is independent of frequency, it is also a form of white noise. It should be noted that the actual noise observed across a resistor will be larger than that predicted by the above equation due to other thermal processes (such as the continuous generation and recombination of carriers) that are occurring in addition to electron thermal motion. Sometimes this additional noise is accounted for by substituting a "noise temperature" into the above equation, and this noise temperature can be much higher than the actual temperature of the resistor.

### Flicker or 1/f noise

Many semiconductor devices exhibit a type of noise that is much greater at low frequencies than that expected by shot or thermal noise. This type of noise has a spectral density function that can be described by the equation shown below:

$$S_i(f) \alpha \frac{1}{f^n}$$

, where  $0 < n < 2$

In most cases, n is very close to 1. Various types of noise with a 1/f dependency occur in nature, and they are actively studied in many scientific fields. In electronics, 1/f noise is typically referred to as flicker noise, and it is caused by the presence of a direct electric current. You may also see 1/f noise referred to as pink noise, to emphasize its intermediate position between white noise (which has no frequency dependence) and red or Brownian noise (which has  $1/f^2$  frequency dependence).

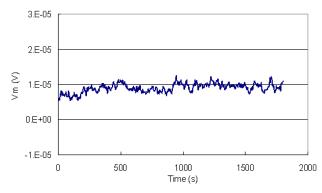

### Random Telegraph Noise (RTN)

Random telegraph noise (also known as burst noise or popcorn noise) manifests itself as fluctuations in the drain current of a MOSFET device under active bias. The root cause of RTN is attributed to the trapping and detrapping of electrons, and when RTN occurs, it usually dominates all other low-frequency noise components. Until recently, RTN was mainly the concern of CMOS image sensor manufacturers, where the RTN created white spots in what should have been dark areas. However, as lithographies have continued to shrink, RTN has become of concern to more device manufacturers, since it can sometimes cause an SRAM cell to erroneously flip to its opposite state. Methods and techniques to characterize RTN will be discussed later in this handbook.

### Power line cycle noise

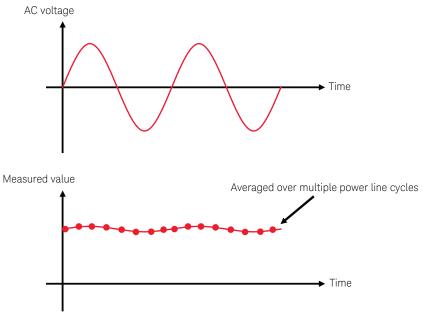

One of the most common sources of noise in parametric testing is power line cycle noise. The AC voltage that measurement instrumentation uses for power typically has a frequency of either 50 or 60 Hz (depending on a given country's standards), and this AC voltage creates powerful electromagnetic fields that can superimpose noise on the quantity under measurement. The effects of power line cycle noise can be mitigated through proper shielding; however, as the measurement range decreases, the effects of power line cycle noise become more pronounced. In this case, the only effective means to eliminate power line cycle noise is to average the measurement over one or more power line cycles. Virtually all parametric measurement instruments have this capability. Careful reading of most instrument specifications reveals that their lowest level of measurement resolution actually requires integration over 16 power line cycles. Power line cycle integration will be discussed further in chapter 3.

# Chapter 3

## Source/Monitor Unit (SMU) Fundamentals

"You do not really understand something unless you can explain it to your grandmother." - Albert Einstein

### SMU overview

### Introduction

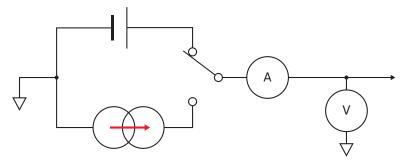

The primary measurement resource for parametric test is the source/monitor unit or SMU. This is sometimes also referred to as a source/measurement unit, although the acronym ends up the same. The SMU can force voltage or current and simultaneously measure voltage and/or current. The diagram below shows a simplified SMU equivalent circuit:

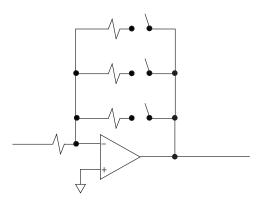

Figure 3.1. Simplified SMU schematic.

Since SMUs must measure very low currents (1 fA or less), they always have triaxial outputs for the reasons discussed in the previous chapter.

There are different types of SMUs. The most common SMU is the medium-power SMU (MPSMU); as the name implies this SMU can supply moderate levels of voltage and current ( $\pm 100 \text{ V}$  and  $\pm 100 \text{ mA}$ ). It also has current measurement resolution down to 10 fA. For precision measurements there is the high-resolution SMU (HRSMU); this SMU can supply the same current and voltage as the MPSMU, but it provides current measurement resolution of 1 fA or less and voltage measurement resolution of 0.5  $\mu$ V. The high-power SMU (HPSMU) is for situations requiring larger currents and voltages than that supplied by the MPSMU or HRSMU; this SMU can supply current up to  $\pm 1$  A and voltages up to  $\pm 200 \text{ V}$ , and the measurement resolution capability is similar to that of a MPSMU.

In addition to the basic SMU types just mentioned, the B1500A MPSMU and HRSMU support an additional module that enables them to achieve current measurement resolutions of 0.1 femtoamps (100 attoamps). In order to achieve this level of current measurement resolution, the actual measurement unit has to be placed in close proximity to the device under test (DUT). This means that this module has to be mounted onto the wafer prober and connected back to an SMU installed in the parameter analyzer mainframe via some sort of cabling arrangement. In the case of the Keysight B1500A, this module is called the atto-sense and switch unit (ASU). Besides being able to provide 0.1 fA current measurement resolution, the ASU also has some switching capabilities that will be discussed further in chapter 4.

### Introduction (continued)

| Module                         | HPSMU  | MPSMU   | HRSMU   | ASU     |

|--------------------------------|--------|---------|---------|---------|

| Maximum Force Voltage          | ±200 V | ±100 V  | ±100 V  | ±100 V  |

| Maximum Force Current          | ±1 A   | ±100 mA | ±100 mA | ±100 mA |

| Voltage Measurement Resolution | 2 μV   | 0.5 μV  | 0.5 μV  | 0.5 μV  |

| Current Measurement Resolution | 10 fA  | 10 fA   | 1 fA    | 0.1 fA  |

Figure 3.2. The key specifications of the basic SMU module types.

The B1505A and B1506A support two unique types of internal SMU modules. The high-current SMU (HCSMU) operates in two modes: DC and pulsed. In DC mode the HCSMU can source up to ±1 A at 40 V; in pulsed mode the HCSMU can source up to ±20 A at 20 V. The HCSMU has a unique output configuration and cabling requirements that will be discussed later in this chapter. The high-voltage SMU (HVSMU) can source up to 3000 V at 4 mA. Due to its high output voltage capability, the HVSMU requires a high-voltage triaxial cable that has a special screw-on triaxial connector. This ensures that a standard triaxial cable cannot accidentally be used with this module.

| Module                         | HCSMU                        | HVSMU                                |

|--------------------------------|------------------------------|--------------------------------------|

| Maximum force voltage          | ±40 V (DC)<br>±20 V (Pulsed) | ±3000 V                              |

| Maximum force current          | ±1 A (DC)<br>±20 A (Pulsed)  | ±8 mA at ±1500 V<br>±4 mA at ±3000 V |

| Voltage measurement resolution | 200 nV                       | 200 μV                               |

| Current measurement resolution | 10 pA                        | 10 fA                                |

Figure 3.3. The key specifications of the HCSMU and HVSMU (B1505A and B1506A only).

Note: For the HVSMU module, the output voltage and current must be of the same polarity.

The B1500A, B1505A and B1506A support one additional special SMU type, which is the medium current SMU (MCSMU). Although the MCSMU is supported in both the B1500A and B1505A/B1506A mainframes, its purpose for these products is different. In the B1500A, the MCSMU functions as a standalone module, and it provides two main benefits. The first benefit is that it supports  $50~\mu s$  SMU pulsing, which is 10~times narrower than the pulses that can be generated by the B1500A MPSMU, HPSMU and HRSMU modules. The second benefit is that it supports the Oscilloscope View feature in the Tracer Test Mode, which allows the user to verify pulsed measurement waveforms right on the front panel of the B1500A. In contrast, in the B1505A and B1506A the MCSMU module is not intended to be used by itself but rather it is used as a control SMU for other modules. All of these features will be explained in greater detail in later sections of this handbook.

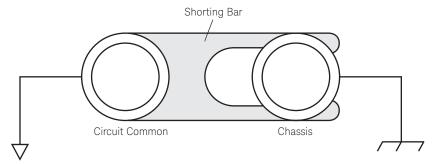

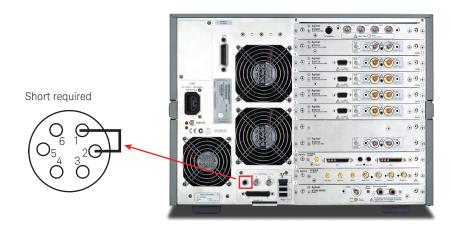

Except for the HCSMU and MCSMU, SMUs are single-ended devices with one end always tied to a common internal reference point. The SMU reference level is normally tied to chassis ground via an external shorting bar, but this shorting bar can be removed and the SMU reference can be tied to an external voltage (up to 42 V maximum) using various types of connectors.

### Introduction (continued)

Figure 3.4. You can remove the shorting bar from the chassis ground to float the SMU circuit common.

Note: In the case of the B2900A, the SMU channels are tied to chassis ground via an internal relay. This relay is normally closed, but it can be opened using a software command to allow for floating SMU measurements.

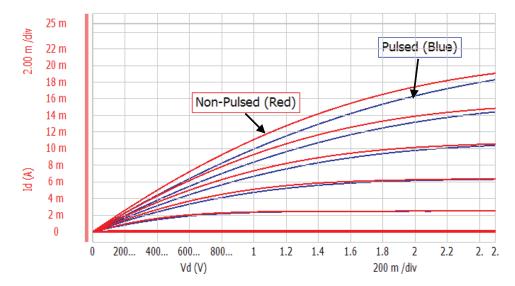

All SMUs have some pulsing capability during sweep measurements (used to prevent heating on thermally sensitive devices), and SMUs can also make time sampling measurements. However, the pulsing and time sampling capabilities of SMUs are relatively slow (in the microsecond range). It is important to understand when you can use an SMU to make pulsed measurements, and when you need the pulsing capabilities of a semiconductor pulse generator unit (SPGU) or waveform generator/fast measurement unit (WGFMU) (both of which have nanosecond pulsing capabilities). These different solutions will be covered in detail when we discuss making high-speed measurements in chapter 5. Because of their relatively slow pulsing capabilities, triaxial cables and DC probes can be used with SMUs when performing pulsed and time sampling measurements. However, as will be discussed in subsequent chapters, pulsing and fast measurements made with other types of modules (such as the HV-SPGU and WGFMU modules) require specialized cables and RF probes for optimal measurement results.

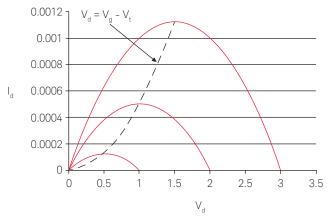

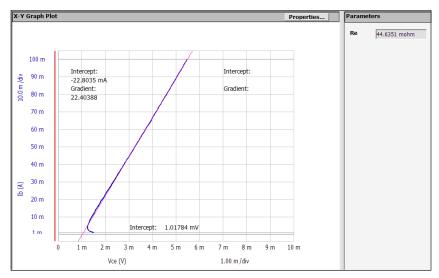

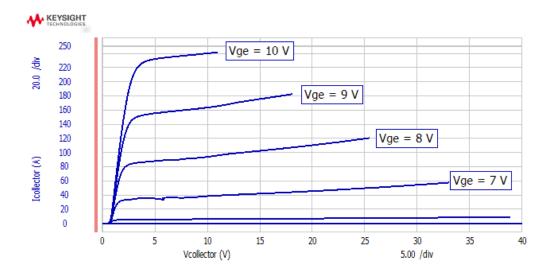

Figure 3.5. SMUs can be pulsed during sweep measurements to eliminate device self-heating effects that can distort measurement results as shown in the above MOSFET current drain versus voltage drain plots.

### SMU operation modes and settings

SMUs have three basic modes of operation: voltage source, current source and common. In common mode, the SMU acts as a 0 V voltage source, it cannot perform any measurement, and the current compliance is automatically set to the SMU's maximum value. In addition, for sweep measurements, you can set SMUs in voltage pulse or current pulse mode to prevent device self-heating on thermally sensitive devices.

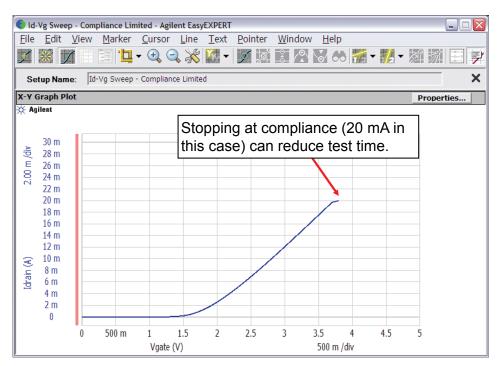

SMUs have the ability to specify a compliance setting. The compliance setting is always opposite to that of the source setting of the SMU (that is, current compliance when the SMU is in voltage source mode and voltage compliance when the SMU is in current source mode). When an SMU reaches compliance, it acts as a constant voltage or current source. The compliance feature prevents inadvertent device damage by not allowing the measured quantity to exceed the specified compliance value. In addition, on swept sources, it is also possible to specify power compliance. The power compliance prevents the total power output by the SMU from exceeding the specified power compliance value. If both standard and power compliance are specified, then the SMU will never exceed whatever is the lower of these two settings.

On the "Measurement Setup" tab in Keysight EasyEXPERT software you can specify the various compliance settings for each SMU. In addition, there is a "Sweep status" selection menu that allows you to select either "CONTINUE AT ANY" or "STOP AT ANY ABNORMAL". The "continue at any setting" will continue making measurements regardless of any abnormal conditions that may occur (such as a measurement error, reaching compliance, etc.). Conversely, the "stop at any abnormal" setting will immediately halt testing when any of these conditions occurs. Especially in the case of automated measurements (where you are not monitoring the status of the instrument as it measures), the stop at any abnormal feature can be valuable in reducing needless measurement time. An example of this is shown below.

Figure 3.6. By using the **stop at any abnormal** setting you can automatically halt testing when compliance is reached and avoid needlessly continuing a measurement.

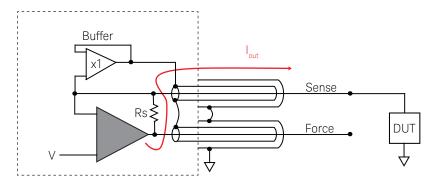

## SMU force and sense outputs

The situations requiring Kelvin measurements and the basic theory of Kelvin measurement have already been discussed. By separating the force and sense lines you can eliminate the effect of cable resistance from your parametric measurement. To make this task easier, modern SMUs are designed with both force and sense outputs. The following illustration shows the output configuration of a Kelvin SMU.

Figure 3.7. Simplified Kelvin SMU output circuit.

The great benefit of a Kelvin SMU configuration is that you only need two SMUs to perform a Kelvin measurement as shown below.

Figure 3.8. Making a Kelvin measurement on a resistor with two Kelvin SMUs.

It is important to point out that the force and sense lines should be shorted together as close to the DUT as possible (for example by using Kelvin triaxial positioners), since the effects of any additional resistance beyond the shorting point will not be eliminated from the measurement.

#### SMU force and sense outputs (continued)

Many situations do not require Kelvin measurements, so it is important to understand which SMU output to use when not making Kelvin measurements. If not making Kelvin measurements and using only one output of the SMU then you must always use the **force** output. The force and sense lines are internally connected via a resistor and this internal sense point is a high-impedance node, so the SMU has no problems with monitoring the current and voltage on the force output when only using the force line. However, consider what happens if you use only the sense line. In this case the entire current flowing out (or in) through the sense output has to pass through the internal resistor as shown below.

Figure 3.9. The problem with using only the sense line on a Kelvin SMU.

This will distort all of your measurement results and give completely incorrect measurement data. Note: Never connect only the sense line of a Kelvin SMU to the DUT.

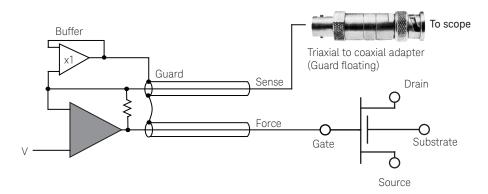

It is possible to use the SMU sense line as a buffered voltage monitor of the SMU force line in non-Kelvin measurement situations. The most common case is when you are driving the gate of a MOSFET with the force line of an SMU and you want to monitor the gate voltage. Using a triaxial to coaxial adapter (guard floating) you can connect the SMU sense line directly to the oscilloscope input as shown below.

Figure 3.10. If the sense line of the SMU is not used, then you can connect it to an oscilloscope to monitor the SMU output.

Note: When placing any loading onto the output of an SMU you have to be careful, as there is a specified limit on the capacitance. Attaching large capacitive loads to SMU outputs can result in oscillation, so you need to make sure that your oscilloscope input capacitance does not exceed the specified limit of SMU load capacitance.

#### Understanding the ground unit

The ground unit (GNDU) is a special type of SMU that does not have any measurement capabilities. Its purpose is to provide an active ground to use with the other instrument resources. The ground unit will always maintain a voltage of zero volts as long as you do not exceed the maximum specified value that it can sink or source (for example  $\pm 4.2$  A in the case of the Keysight B1500A, B1505A and B1506A). The benefit of using an active ground versus a passive ground should be obvious: you do not need to worry about the ohmic drop from large currents distorting your measurement results (at least if you maintain a Kelvin environment).

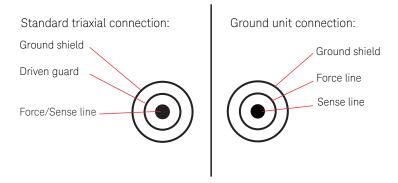

The configuration of the ground unit is a source of confusion for many users. This confusion is understandable given that, while the ground unit looks like a standard triaxial connection, it is not. The ground unit has the configuration that it does for historical reasons; in the past there simply was not enough room on some instruments for a separate force and sense line for the ground unit. Therefore, the force and sense lines were merged into a single connector. A comparison of the connections on a standard triaxial cable and the ground unit is shown below.

Figure 3.11. Comparison of standard triaxial connection and the ground unit.

The ground unit can have the configuration that it does because the potential of the force and sense lines is always at zero volts, so there is no need to isolate them from the outer ground shield to prevent leakage currents. It should be noted that the ground unit is the only case in which this scheme can work.

## Understanding the ground unit (continued)

The illustration shown below highlights the problem with connecting up the ground unit like a standard triaxial output.

Figure 3.12. The problem with connecting up the ground unit like a standard triaxial connection.

As you can see, connecting up the ground unit like a standard triaxial connection is equivalent to connecting up only to the sense line on a Kelvin SMU. Obviously, this will lead to erroneous measurement results.

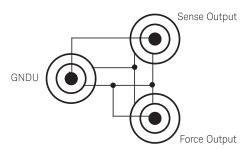

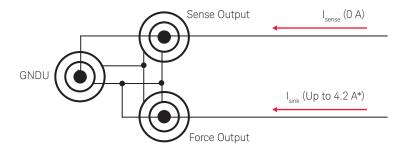

The following illustration shows the proper way to connect the ground unit to standard Kelvin SMU connections. Keysight can supply a ground unit to Kelvin adapter, the N1254A-100, which converts the ground unit output into the force and sense outputs as shown below.

Figure 3.13. The proper way to connect a ground unit to standard triaxial connections.

#### Understanding the ground unit (continued)

Of course, the ground unit adapter can be used with only the force output connected just like a standard SMU. However, you need to be careful when doing this. Assumedly one reason that you are using the ground unit is to sink large currents, and large currents innately require a Kelvin connection (using both the force and sense outputs). Therefore, especially if you are using the ground unit to sink current from one or more high-power SMUs, it is highly recommended that you connect the ground unit in a Kelvin configuration as shown below.

\*B1500A, B1505A & B1506A

Figure 3.14. The ground unit should be used in a Kelvin configuration when sinking large currents.

Note: Keysight makes a special triaxial cable designed to be used with the force output of the ground unit. This cable can handle the 4.2 amps maximum current. The part numbers are 16493L-001 (1.5 m), 16493L-002 (3 m) and 16493L-003 (5 m).

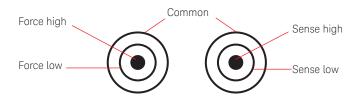

# High current SMU connections (B1505A and B1506A)

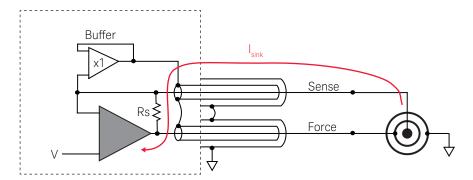

As was mentioned earlier, the high current SMU (HCSMU) is a special module available only for the B1505A and the B1506A. Its structure is similar to that of an SMU except that it can source up to 20 A of current (pulsed). Because no other module can sink this much current, the HCSMU also has to have the ability to sink its own current. This gives the HCSMU a unique output configuration.

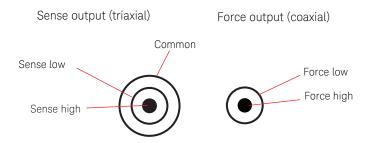

Figure 3.15. The output connections on the HCSMU.

The force lines of the HCSMU do not perform any measurement so they do not require any shielding and they can be coaxial. On the other hand, the sense lines of the HCSMU do perform measurement so they require shielding and they need to be triaxial. Fortunately, this arrangement makes it impossible to confuse the two outputs.

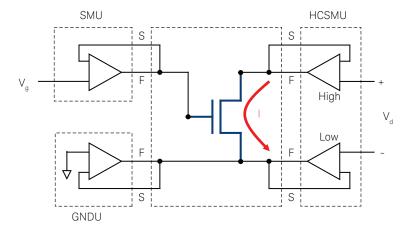

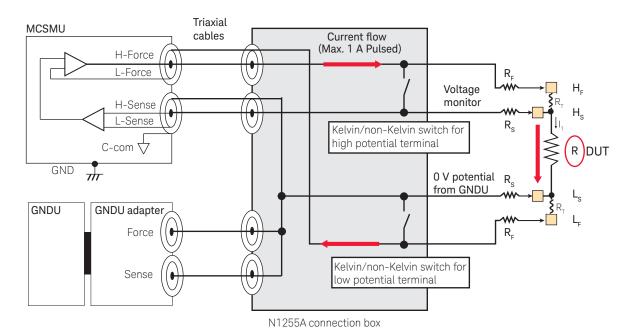

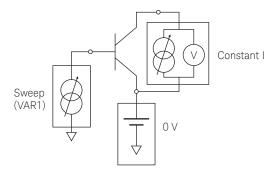

The HCSMU module is floating and is not tied internally to the instrument ground. This means that its low force and sense outputs must be tied to a reference level (normally the ground unit) when making a measurement. An example MOSFET measurement using the HCSMU is shown below.

Figure 3.16. The HCSMU needs to have its low outputs (force low and sense low) tied to a known voltage reference when making a measurement.

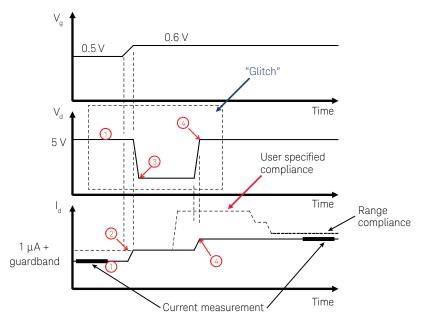

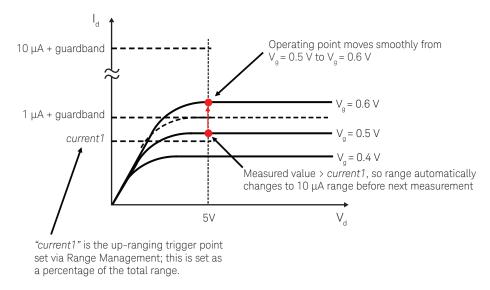

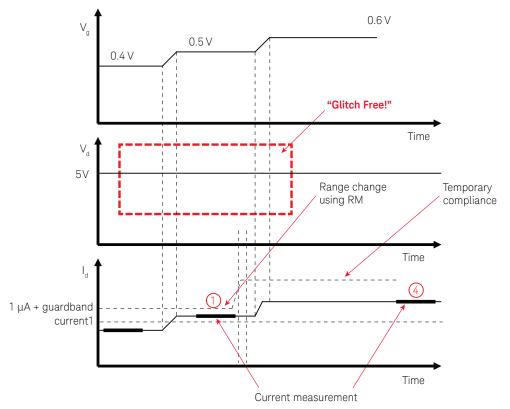

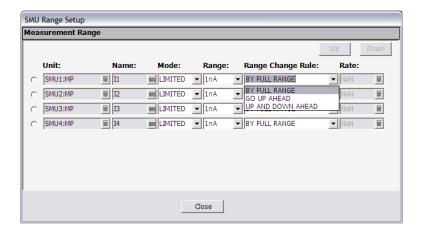

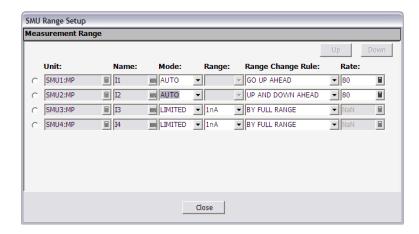

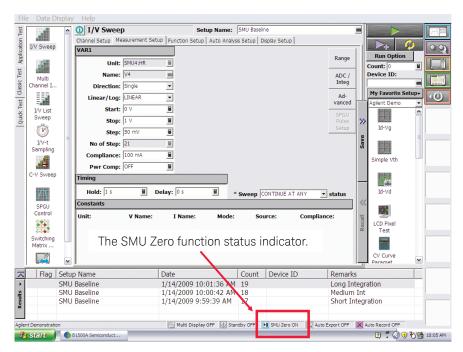

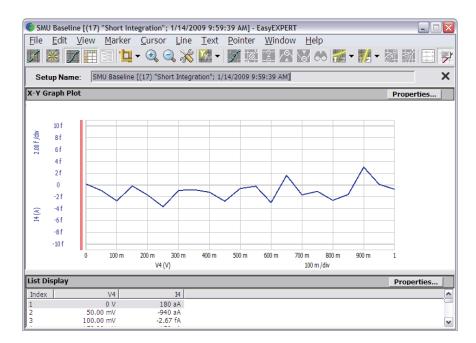

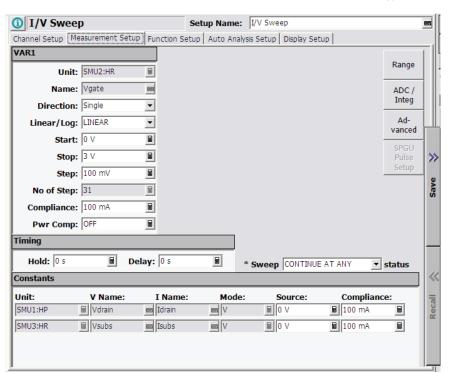

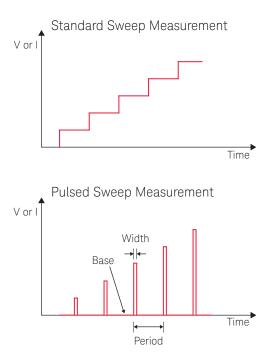

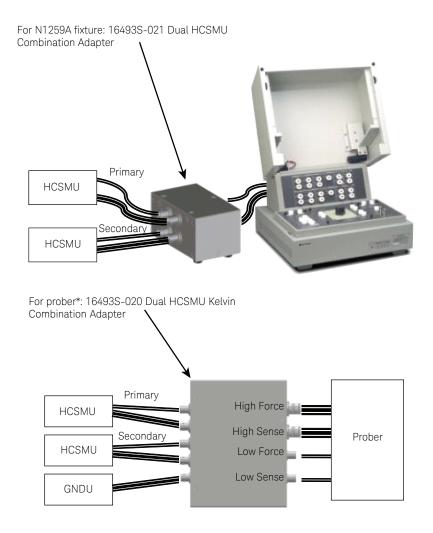

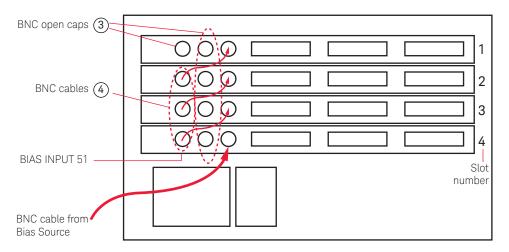

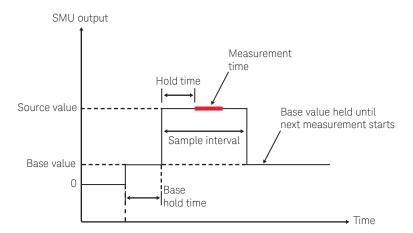

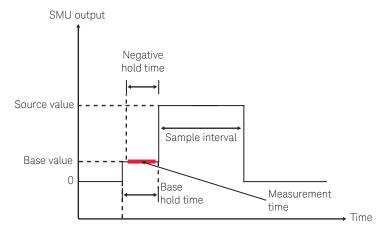

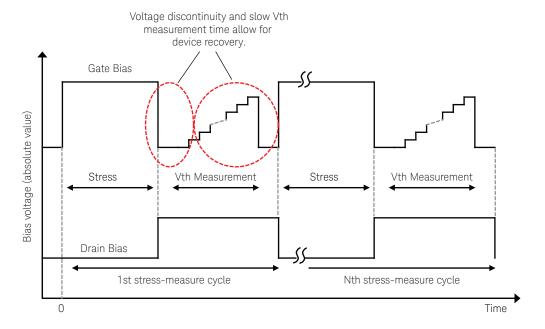

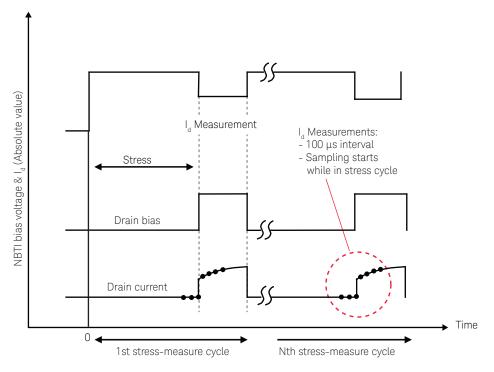

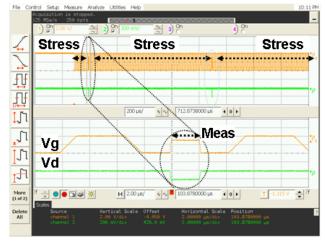

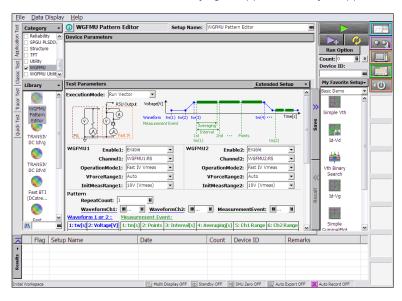

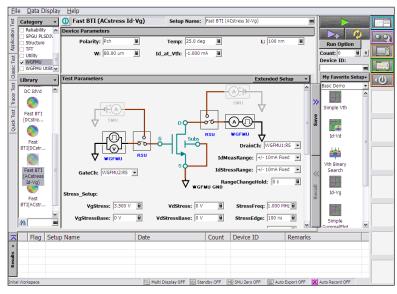

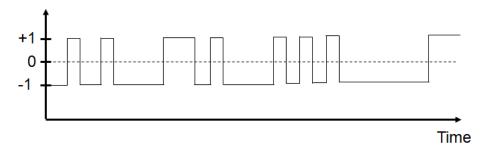

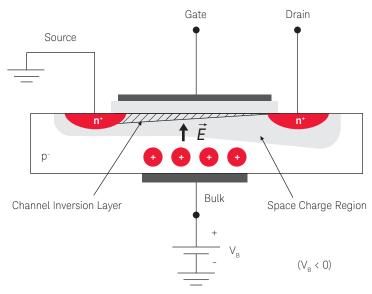

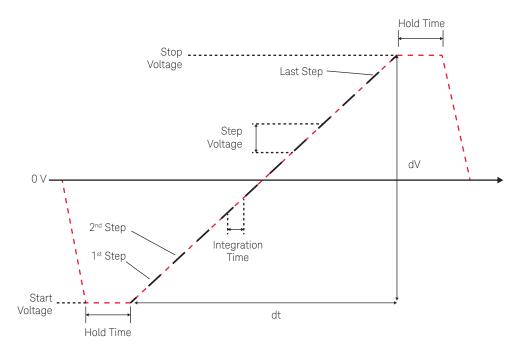

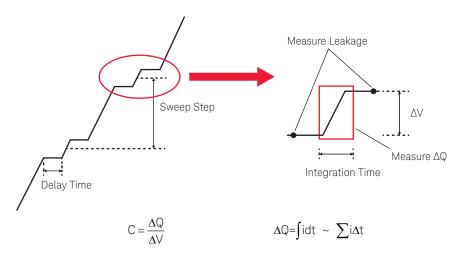

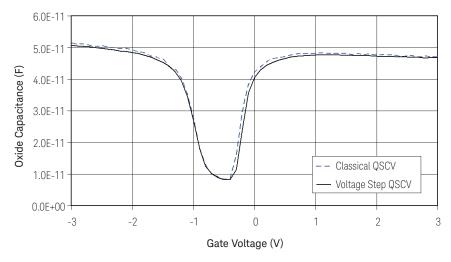

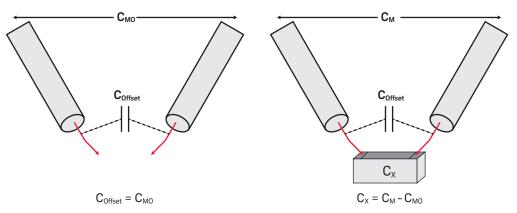

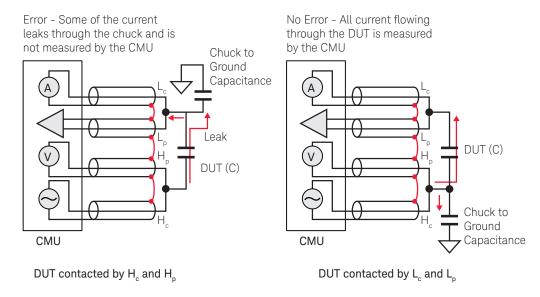

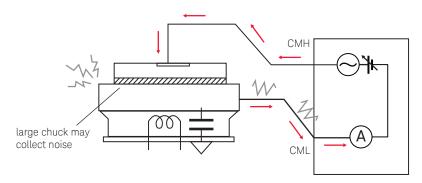

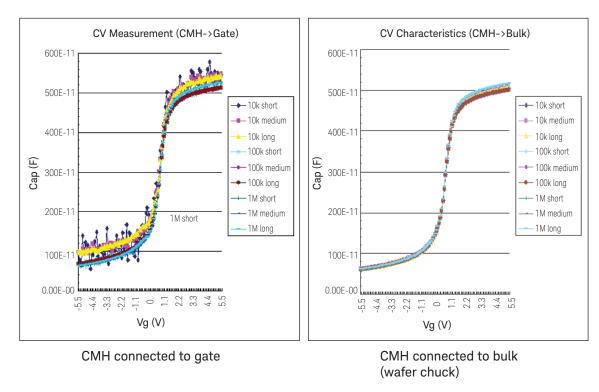

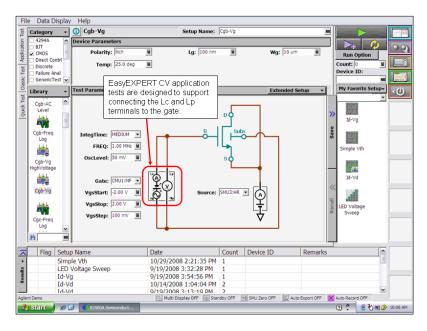

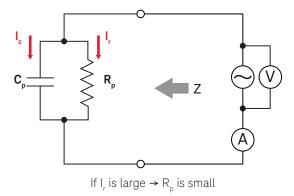

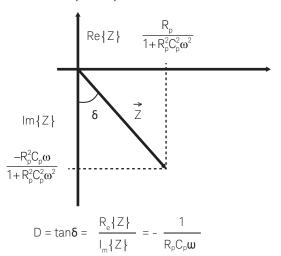

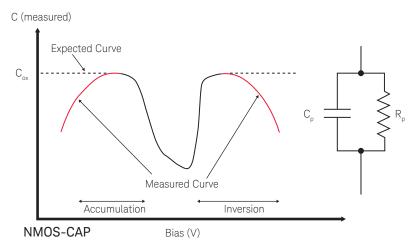

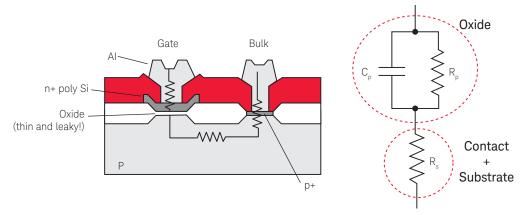

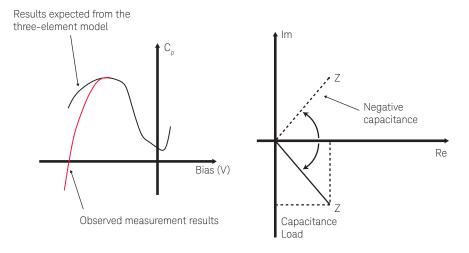

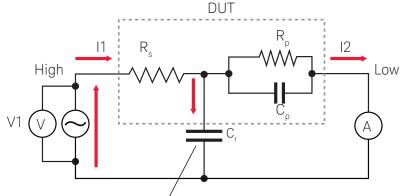

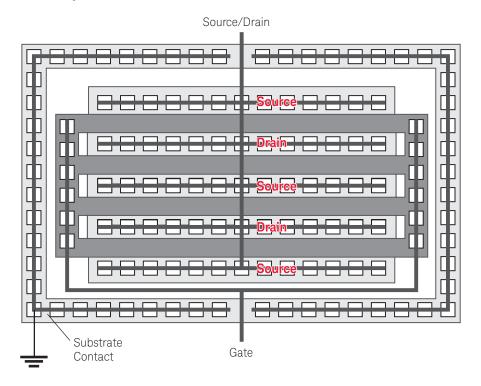

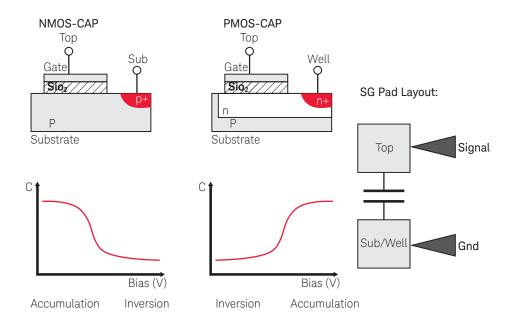

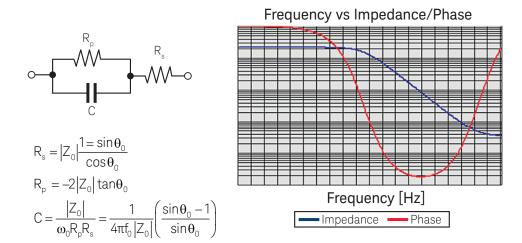

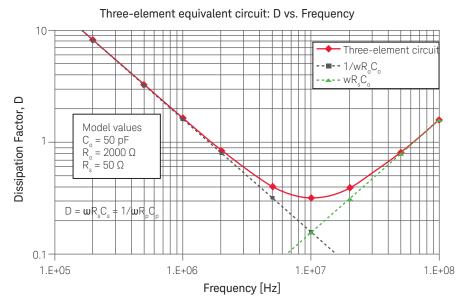

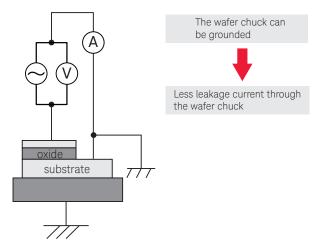

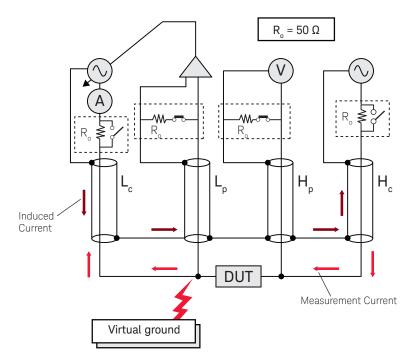

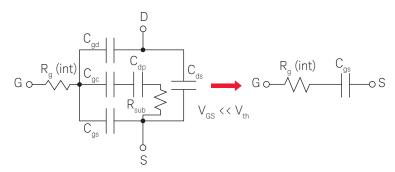

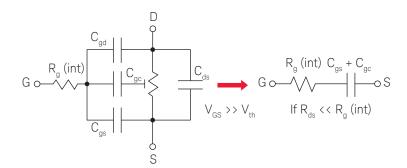

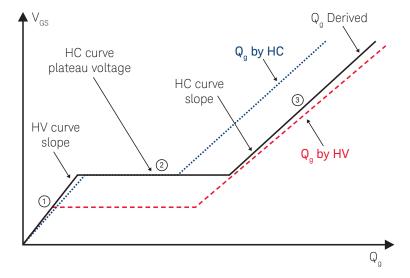

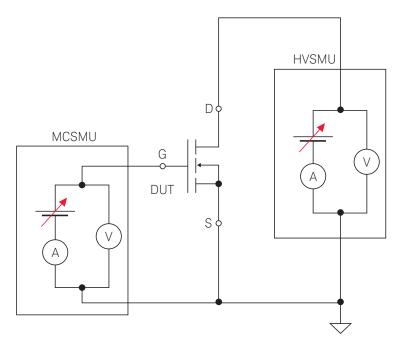

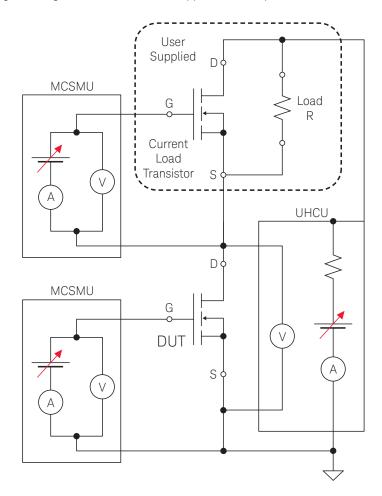

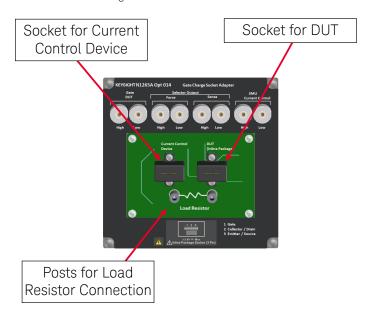

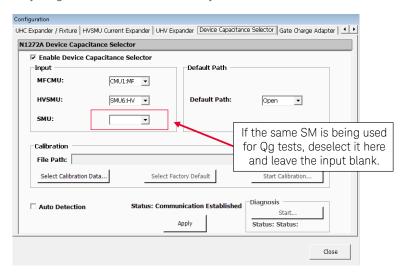

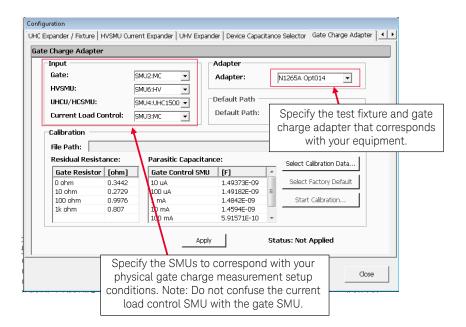

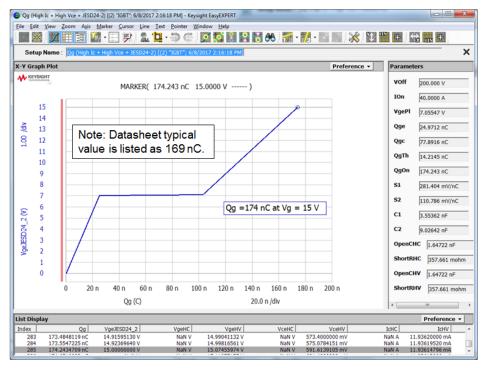

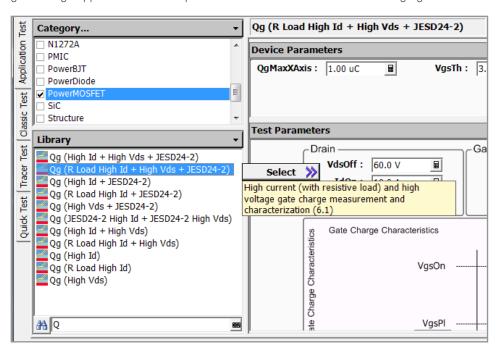

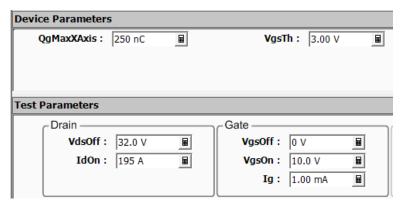

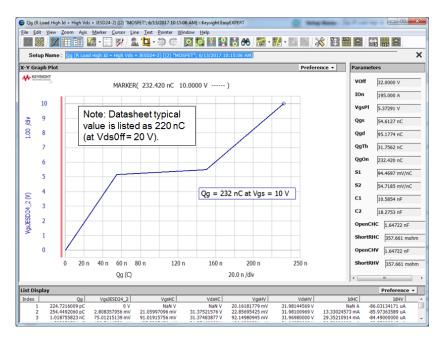

When you are using the HCSMU with the N1259A or N1265A high-power test fixtures, both units take care of correctly separating out the HCSMU connections. However, you need to make sure that you use the correct cables and adapters when connecting the HCSMU up to a wafer prober. Keysight supplies a variety of adapters and connectors for this purpose. This will be covered in greater detail when we discuss making on-wafer measurements in chapter 4.